## A-SSCC 2007

## The 3rd IEEE Asian Solid-State Circuits Conference

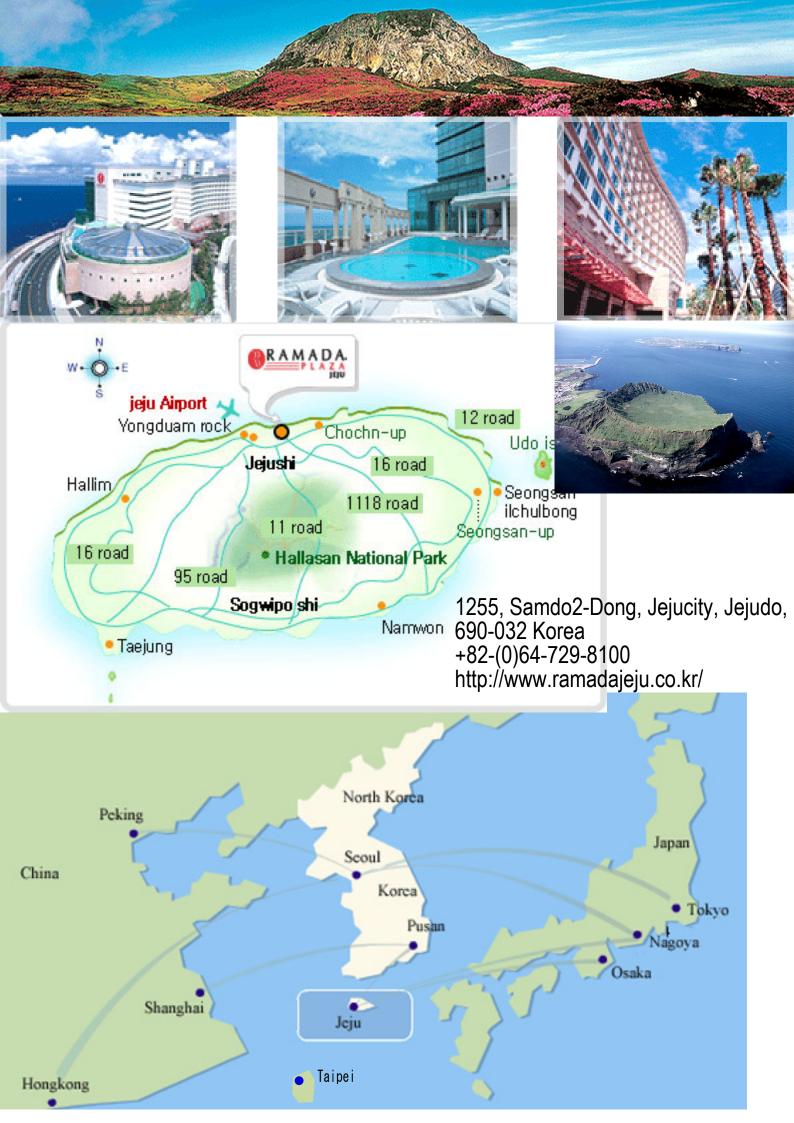

12 - 14 November 2007 - Jeju, Korea

# Advance Program

www.a-sscc.org

| Time        | Room 1<br>(Ramada Ballroom 1)<br>[Tutorial I]<br>An Introduction to Analog to Dicital Converter Design                        | Room 2<br>(Ramada Ballroom 2)<br>[Tutorial II]<br>Silicon mm-wave IC design                        |                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|

| 9:00-10:20  |                                                                                                                               | Huei Wang(NTU)                                                                                     |                             |

| 04.0        | [Tutorial I]                                                                                                                  |                                                                                                    |                             |

| 10:40-12:00 | An Introduction to Analog to Digital Converter Design<br>– Old problems and New Challenges<br>David Robertson(Analog Devices) | Silicon mm-wave IC design<br>Huei Wang(NTU)                                                        |                             |

| 12:00-13:00 | Lun                                                                                                                           | Lunch                                                                                              |                             |

|             | [Tutorial III]                                                                                                                | [Tutorial IV]                                                                                      | <b>On-Site Registration</b> |

| 13:00-14:20 | Advanced leakage reduction Techniques<br>Rusu Stefan(Intel)                                                                   | Low energy CMOS systems for body sensor network<br>and ubiquitous healthcare<br>Hoi-Jun Yoo(KAIST) | (9am-6pm)                   |

| 14:20-14:40 | Bre                                                                                                                           | Break                                                                                              |                             |

|             | [Tutorial III]                                                                                                                | [Tutorial IV]                                                                                      |                             |

| 14:40-16:00 | Advanced leakage reduction Techniques<br>Rusu Stefan(Intel)                                                                   | Low energy CMOS systems for body sensor network<br>and ubiquitous healthcare<br>Hoi-Jun Yoo(KAIST) |                             |

| 16:00-17:00 | SDC E                                                                                                                         | SDC Exhibits                                                                                       |                             |

| 18:00-20:00 | Recei                                                                                                                         | Reception                                                                                          |                             |

A-SSCC 2007 Conference Program: November 12 (Mon.), 2007

| Time        | Room 1<br>(Ramada Ballroom 1)                                                                                                                                                             | Room 2<br>(Ramada Ballroom 2)                                                                                                          | Room 3<br>(Ramada Ballroom 3)                                                                                                                                                         | Room 4<br>(Ramada Ballroom 4)                                                                         |                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|

| 9:00-9:05   |                                                                                                                                                                                           |                                                                                                                                        | Opening                                                                                                                                                                               |                                                                                                       |                |

|             |                                                                                                                                                                                           |                                                                                                                                        | [Plenary Speech 1]                                                                                                                                                                    |                                                                                                       |                |

| 9:05-9:50   |                                                                                                                                                                                           | <b>The Strategic Con</b><br>Dr. Heegook Le                                                                                             | The Strategic Considerations for Digital-TV System-on-Chip Products<br>Dr. Heegook Lee (President and CTO, LG Electronics Inc., Korea)                                                | Chip Products<br>Ic., Korea)                                                                          |                |

|             |                                                                                                                                                                                           |                                                                                                                                        | [Plenary Speech 2]                                                                                                                                                                    |                                                                                                       |                |

| 9:50-10:35  |                                                                                                                                                                                           | Convergence a<br>Mr. Satoru                                                                                                            | Convergence and Divergence in Parallel for the Ubiquitous Era<br>Mr. Satoru Ito (Chairman and CEO, Renesas Tach., Japan)                                                              | luitous Era<br>Japan)                                                                                 |                |

| 10:35-11:05 |                                                                                                                                                                                           |                                                                                                                                        | Break / SDC                                                                                                                                                                           |                                                                                                       |                |

|             |                                                                                                                                                                                           | Industry                                                                                                                               | Industry Program                                                                                                                                                                      |                                                                                                       |                |

| 11:05-12:45 | Session H<br>Local FC Trend & Comp                                                                                                                                                        | Session I-I<br>Local FC Trend & Computing Circuits                                                                                     | Session I-II<br>Storage & High Speed Interface                                                                                                                                        | on I-II<br>Speed Interface                                                                            |                |

|             | Co-Chairs: S. Rusu(Intel), K. Wong(Intel), B. Jin Yoon(                                                                                                                                   | Vong(Intel), B. Jin Yoon(ETRI)                                                                                                         | Co-Chairs: S. Wei(Phoenix Microelectronics), J. Kim(Rambus)                                                                                                                           | oelectronics), J. Kim(Rambus)                                                                         |                |

| 12:45-13:45 |                                                                                                                                                                                           | Fu                                                                                                                                     | Lunch                                                                                                                                                                                 |                                                                                                       |                |

|             | Session 1<br>Power Efficient Circuits and<br>Ayatems                                                                                                                                      | Session 2<br>Clock & Frequency Generation                                                                                              | Session 3<br>High Performance Amplifiers and<br>Varactor-Less VCO                                                                                                                     | Session 4<br>Emerging Trends in Proximity<br>Interface                                                |                |

| 13:45-15:50 | Co-Chairs:<br>H. Kabuo(Panasonic),<br>M.H. Sunwoo(Ajou Univ.)                                                                                                                             | Co-Chairs: K. Mashiko(STARC), S.H.<br>Cho(KAIST)                                                                                       | Co-Chairs: K. Mashiko(STARC), S.H. Co-Chairs: CN. Kuo(Nat'l Chao Tung<br>Cho(KAIST)<br>BS. Kim(SungKyunKwan Univ.)                                                                    | Co-Chairs: C.P. Yue(UC Santa<br>Barbara),<br>K. Kotani(Tohoku Univ.)                                  | SDC / Exhibits |

| 15:50-16:00 |                                                                                                                                                                                           | Br                                                                                                                                     | Break                                                                                                                                                                                 |                                                                                                       |                |

| 16:00-16:45 |                                                                                                                                                                                           | Speci<br>"How to Present a (                                                                                                           | Special Talk<br>"How to Present a Good ISSCC Paper"                                                                                                                                   |                                                                                                       |                |

|             |                                                                                                                                                                                           | Dr. Jan Van der Spiegel(Profes                                                                                                         | Spiegel(Professor, University of Pennsylvania)                                                                                                                                        |                                                                                                       |                |

| 16:45-16:50 |                                                                                                                                                                                           | Br                                                                                                                                     | Break                                                                                                                                                                                 |                                                                                                       |                |

|             |                                                                                                                                                                                           | Panel Di                                                                                                                               | Panel Discussion                                                                                                                                                                      |                                                                                                       |                |

| 16:50-18:30 | "SoC or SiP : What is the Best Solution in IC Business for Ubiquitous<br>Mobile Platforms?"<br>Organizer: Tadahiro Kuroda(Keio Univ.),Joungho Kim(KAIST)<br>Moderator: Joungho Kim(KAIST) | Best Solution in IC Business for Ubiquitous<br>Mobile Platforms?"<br>Kuroda(Keio Univ.),Joungho Kim(KAIST)<br>ator: Joungho Kim(KAIST) | "Display Driver IC's: Next Technology and Market Trends"<br>Organizer: Tadahiro Kuroda, Keio Univ.(Japan), Oh-Kyong Kwon(Hanyang<br>Univ.)<br>Moderator: Oh-Kyong Kwon(Hanyang Univ.) | <b>:hnology and Market Trends</b> "<br>v.(Japan), Oh-Kyong Kwon(Hanyang<br>v.)<br>Kwon(Hanyang Univ.) |                |

| 19:00-21:00 |                                                                                                                                                                                           |                                                                                                                                        | Banquet                                                                                                                                                                               |                                                                                                       |                |

|             |                                                                                                                                                                                           |                                                                                                                                        |                                                                                                                                                                                       |                                                                                                       |                |

A-SSCC 2007 Conference Program: November 13 (Tue.), 2007

A-SSCC 2007 Conference Program: November 14 (Wed.), 2007

|                               |                                                                                                                                                          |                                                                                                 |             |                                                                   |                                                              |             |                                                                              | Exhib<br>its                                                   |             |                                                                 |                                                                         |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|--------------------------------------------------------------|-------------|------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|-----------------------------------------------------------------|-------------------------------------------------------------------------|

| Room 5<br>(Udo Hall)          | ı, Chairman, UMC, Taiwan)                                                                                                                                | . Leuven., Belgium)                                                                             |             | Session 9 - ETA<br>"Emerging Circuit<br>Technologies and Sensing" | Co-Chairs: H. Mizuno(Hitachi),<br>A. Keshavarzi(Intel)       |             |                                                                              |                                                                |             |                                                                 |                                                                         |

| Room 4<br>(Ramada Ballroom 4) | iconductor Industry" (Dr. Jackson Hu                                                                                                                     | in Nanometer CMOS Technologies" (Dr. Wily Sansen, Professor, Katholieke Univ. Leuven., Belgium) |             | Session 8 - ADC<br>"High-Performance ADCs"                        | Co-Chairs: SH. Lee(Sogang Univ.),<br>M. Otsuka(Renesas)      |             | Session 13 - ADC<br>"High-Performance ADCs and<br>Power Management Circuits" | Co-Chairs: H. Onodera(Kyoto Univ.),<br>J. Choi(Univ. of Seoul) |             | Session 17 - ADC<br>"Analog Techniques"                         | Co-Chairs: K. Iizuka(Sharp),<br>S.I. Liu(Naťl Taiwan Univ.)             |

| Room 3<br>(Ramada Ballroom 3) | Trends and Their Impact on the Sem                                                                                                                       | ometer CMOS Technologies" (Dr. Wil)                                                             | Break       | Session 7 - MEM<br>"Memory"                                       | Co-Chairs: JB. Lee(Samsung), T.<br>Yabe(Toshiba)             | Ich         | Session 12 - RF<br>"Freguency Divider and Multiplier"                        | Co-Chairs: R. Kim(Matsushita), H.<br>Luong(HKUST)              | ak          | Session 16 - RF<br>"Oscillators and PLL"                        | Co-Chairs: H. Shin(Kwangwoon<br>Univ.),<br>M. Fujishima(Univ. of Tokyo) |

| Room 2<br>(Ramada Ballroom 2) | [Plenary Speech 3] "Recent Business Models and Technology Trends and Their Impact on the Semiconductor Industry" (Dr. Jackson Hu, Chairman, UMC, Taiwan) | [Plenary Speech 4] "Analog Design Challenges in Nanc                                            |             | Session 6 - MSP<br>"Multimedia Signal Processing"                 | Co-Chairs: H. Noda(Renesas), R.<br>Woo(LG Electronics)       | Lunch       | Session 11 - DCS<br>"Digital Circuits for Power, Clock<br>and Noise"         | Co-Chairs: M. Ikeda(Univ. of Tokyo),<br>KS. Min(Kookmin Univ.) | Break       | Session 15 - WW/ADC<br>"Multi-Gigabit Receiver<br>Techniques"   | Co-Chairs: C. W. Kim(Korea Univ.), M.<br>Nagata(Kobe Univ.)             |

| Room 1<br>(Ramada Ballroom 1) | [Plenary Speech 3] "Rece                                                                                                                                 | [Plenary Speech 4                                                                               |             | Session 5 - WW<br>"Wireless & Wireline<br>Communication"          | Co-Chairs: T. Cheung(Fujitsu), J.<br>Park(GCT Semiconductor) |             | Session 10 - MSP<br>"Mixed-Signal Circuits for<br>Communications"            | Co-Chairs: K. Arimoto(Renesas),<br>OK. Kwon(Hanyang Univ.)     |             | Session 14 - MSP<br>"Graphics and Reconfigurable<br>Processing" | Co-Chairs: T. Shimizu(Renesas),<br>Y. Park(Samsung)                     |

| Time                          | 9:00-9:45                                                                                                                                                | 9:45-10:30                                                                                      | 10:30-11:05 | 11.05-13.10                                                       |                                                              | 13:10-14:10 | 14-10-16-15                                                                  |                                                                | 16:15-16:30 | 16.30.18.35                                                     |                                                                         |

#### Session P-1 Plenary Speech 1 November 13, 2007 (Tue.)

#### **P-1** 9:05-9:50

The Strategic Considerations for Digital-TV System-on-Chip Products Heegook Lee(LG Electronics Inc.)

**Abstract:** The delivery channels for digital TV broadcasting have been diversified: terrestrial, cable, satellite, beyond 3G cellular band and now over the internet. On the physical dimension, popularity of larger screen flat TV's are rapidly growing, while mobile TV technology brought TV viewing to cell phones with QVGA screens. The flexibility of when to watch the programs has been enhanced by PVR technology and set-top boxes with push technology services. And IPTV VOD services offer more flexibility to consumers when and what to watch. Large screen flat TV's are also used for Home Theater environments for Full HD contents. All these developments have occurred within just a few years, and the tasks of developing System-on-Chip (SoC) solutions for the various applications are very challenging. This paper will explore the strategic considerations chip developers have to employ to create the most competitive Digital TV SoC technology and products.

## Session P-2 Plenary Speech 2

November 13, 2007 (Tue.)

#### **P-2** 9:50-10:35

Convergence and Divergence in Parallel for the Ubiquitous Era Satoru Ito(Renesas Tech. Corp.)

Abstract: After having enjoyed the years of staggering growth in the 90's, the semiconductor industry is being matured. Today, it is still a growing industry, at a slower pace, as it continues to expand its reach to cover a growing number of all industries. While miniaturization is still an important consideration for many semiconductor manufacturers, the multitude of complex technology and economical scale limitations are posing as new challenges. Today, there is no single driving force to fuel the growth of the semiconductor industry. Under this new paradigm, it is important re-evaluate the business model of the semiconductor industry, together with two keywords, "Convergence" and Divergence." "Convergence" enables utilization of various application contents beyond time and space, allowing consumers to access data from anywhere, anytime. On the other hand, "Divergence" accelerates segmentation, bringing solutions such as electronics systems tailored for each individual need and widely distributed networked systems. In the ubiquitous era, these seemingly contradicting elements become the foundation for establishing a new business model. Given the change, what is required for Technology is also changing. What the industry really needs is a system-centric innovation approach centered on software, to enable delivery of a wide spectrum of applications, rather than a conventional hardware-centric approach. In my presentation, I'll discuss how to enable such innovations as well as how to overcome other challenges the industry will be facing in the next several years.

#### Session P-3 Plenary Speech 3 November 14, 2007 (Wed.)

#### **P-3** 9:00-9:45

Recent Business Models and Technology Trends and Their Impact on the Semiconductor Industry Jackson Hu(UMC)

**Abstract:** The semiconductor industry is evolving. IDMs are moving to a "fab-lite" or fabless approach due to skyrocketing development costs for advanced technologies. However, a fab-lite strategy isn't simple to execute. Fabless companies also face pressures caused by limited design resources and their desire for multiple manufacturing sources. New materials and equipment have led to uncertainties that threaten Moore's Law, and design for manufacturability (DFM) has become increasingly critical. Although smaller geometries allow an entire system on a single chip, designers may not have taken full advantage of this in their rush to keep up with Moore's law. The design, EDA and manufacturing communities must re-examine their approach. Generally speaking, there is a capacity surplus for older production technologies. Newcomers who jumped into the foundry industry have realized that fab construction is not that difficult, however, filling the capacity and operating profitably is extremely challenging. In summary, the dynamics of IDM, fabless design companies and foundries will be examined.

#### Session P-4 Plenary Speech 4 November 14, 2007 (Wed.)

#### **P-4** 9:45-10:30

Analog Design Challenges in Nanometer CMOS Technologies Willy Sansen(Katholieke Univ. Leuven)

**Abstract:** In nanometer CMOS technologies, several new effects emerge due to short channel-length effects. Some important ones are velocity saturation and gate leakage currents. As a result improved transistor models are required to allow accurate prediction of analog circuit performance. The transconductance and speed are both limited by velocity saturation. Also noise and mismatch suffer from smaller channel lengths, as a result of the thinner gate oxides used. Moreover the supply voltage is reduced to values below 1 volt, creating new challenges for analog circuit design. This presentation provides a review of these model parameters. It is followed by an overview of amplifiers/filters configurations with both Gate and Bulk drives. Current amplifiers are compared to voltage amplifiers in terms of speed and input noise. A large variety of sub-1 volt circuits for different applications are then presented for sake of illustration.

## Session I-I Industry Session I: Local FC Trend & Computing Circuits November 13, 2007 (Tue.) 11:05-12:45

Session Co-Chairs: Stefan Rusu(Intel), Keng Wong(Intel), Byoung Jin Yoon(ETRI)

**I-I-1** 11:05-11:30

Where is Korea's Fabless Semiconductor Industry Headed? James Hwang (IT-SoC Association, Korea)

**Abstract:** Riding on the boom of handset and system display manufacturing at home, Korea's fabless semiconductor industry has made a sharp increase by leaps and bounds. The sales revenue of the fabless semiconductor companies more than doubled to 1.5 trillion Korean won in 2006, compared to 650 billion Korean won in 2003. Marking an annual average growth of 32 percent, the industry is now around the corner of global jump: by overcoming such issues as a broad range of portfolio set-up, business volume expansion through M&A, market diversification, etc.

#### **I-I-2** 11:30-11:55

Penryn: 45nm Next Generation Intel Core Microarchitecture Varghese George (Intel Corp., USA)

**Abstract:** This paper/presentation will discuss Intel's upcoming Penryn (codename) family of processors which are based on Intel's leading 45nm High-k metal gate silicon process. The paper will cover 1) an overview of the new 45 nm process technology and its benefits utilized in Penryn 2) an overview of the major new architectural features such as the Fast Radix-16 Divider, the new Intel SSE4 instructions and other microarchitecture enhancements for improved performance. 3) Advanced Power management features such as Deep Power Down Technology and Enhanced Intel Dynamic Acceleration Technology 4) Some of the physical design implementation challenges and innovations including efficient organization of the larger L2 cache, Low Power techniques used in the design, Clock and Power distribution, Design for Test and Design for Debug techniques and features, and the Packaging technology used in various family of Penryn products.

#### **I-I-3** 11:55-12:20

Design of a 90nm 4-CPU 4320MIPS SoC with Individually Managed Frequency and 2.4GB/s Multi-master On-chip Interconnect

Osamu Nishii, Itaru Nonomura, Yutaka Yoshida, Kiyoshi Hayase, Shin'ichi Shibahara (Renesas Tech. Corp., Japan), Yoshitaka Tsujimoto, Masashi Takada (Hitachi Ltd., Japan), and Toshihiro Hattori (Renesas Tech. Corp., Japan)

**Abstract:** We have developed a 97.6mm2 SoC that includes four SuperH architecture CPUs and DDR-2 controller with 90nm CMOS for high-performance embedded applications. These four 600MHz CPUs are identical and each has floating point, 32/32KB cache memory, and 152KB local memory. CPUs totally achieve performance of 4320MIPS. Main on-chip 300MHz 64bit bus manages processors access and another dedicated connection holds cache coherency operation. Considering varying processing load, this chip targets both low power consumption (proportional to processing load), and constant on-chip bandwidth. Each processor can be operated different frequencies while keeping on-chip bus frequency

constant. With utilizing this individual core clock distribution scheme, the following designs have been developed: (i) frequency transition control that permits on-chip bus access of other bus master, (ii) light-sleep mode that maintains cache coherency control, (iii) cache snoop control logic that holds cache coherency between multiple frequency processors. The main on-chip interconnect (bus) connects four-processor and other on-chip IPs. The numbers of access master and access slave increase due to processor number. This on-chip bus specification and logic implementation technique achieve 300MHz multi-master operation.

#### **I-I-4** 12:20-12:45

The Niagara2: A Highly Threaded Power Efficient Sparc SOC Gregory Grohoski, Robert Golla, Manish Shah, Paul Jordan, Jeffrey Brooks, Christopher Olson, Mark Luttrell, and Jama Barreh (Sun Microsystems, USA)

Abstract: Niagara2 is a second generation multi-core, multi-threaded 64b Sparc SOC. Niagara2 supports concurrent execution of 64 threads by utilizing eight, 8-threaded Sparc cores which communicate with a 4MB, 8-bank L2 cache through a high bandwidth crossbar. Niagara2 delivers twice the throughput of its predecessor, the UltraSparc T1, in essentially the samepower envelope. Each Sparc core includes two integer execution units, a dedicated floating-point and graphics unit, and a cryptographic unit. Niagara2 has a peak floating-point throughput performance of 11.2 GFLOPS/s. Niagara2 contains one x8 PCI-Express channel, two 10G Ethernet ports with XAUI interfaces, and four memory controllers each controlling 2 FBDIMM channels. Niagara2 achieves a peak memory bandwidth in excess of 60GB/s. Niagara2 is fabricated in an 11 metal, 1.1V, triple-Vt CMOS process. Niagara2 has ~500M transistors on a 342 mm2 die with a power consumption of

## Session I-II Industry Session II: Storage & High Speed Interface November 13, 2007 (Tue.) 11:05-12:45 Session Co-Chairs: Shaojun Wei(Phoenix Microelectronics), Jaeha Kim(Rambus)

#### **I-II-1** 11:05-11:30

SSC - A New Generation of Smart Controller for Mobile Storage Yanhui Yang, Muhua Han, Sudong Yu, and Shaojun Wei (Phoenix Microelectronics, China)

**Abstract:** Personal information storage and data processing are two of the key issues in mobile device product development. SSC give a new solution to solve these handicaps on account of that it is different from traditional SD card, MMC card and USB device. It tries to integrate high performance calculation, large volume memory and some popular flash card interfaces together into one chip, which leads to a new generation of smart controller for mobile storage. SSC can be used in mobile phones, digital camera, and other electronic devices which need not only large storage but also data processing and information management ability. Mega-Byte class SIM is a typical usage. It can provide an attractive and profitable Value-Added-Service (VAS) platform to telecom carriers. Assisted by the new SIM, the mobile phone can largely expand and strengthen it's user experience, WEP service is a excellent practice benefit from it's GUI system to provide renewable applications. A programmable chip platform and flexible software system are absolutely necessarily. This paper will focus on these topics and give some key discussions on smart controller chip and major application software design technology. One successfully developed SoC will be presented also in this paper.

#### I-II-2 11:30-11:55

A PCI-Express Gen2 Transceiver with Adaptive 2-Tap DFE for Up to 12-meter External Cabling Tse-Hsien Yeh, Wei-Yu Wang, Wen-Liang Wang, Yu-Hong Lin, Ying-Lien Cheng, Tsung-Hsin Chou, and Jyhfong Lin (VIA Technologies, Inc., Taiwan)

**Abstract:** The most updated specification of PCI-Express External Cabling 1.0 only specifies Gen1 (2.5Gbps) for short-reach usage. This proposed transceiver architecture not only increases the link rate from Gen1 to Gen2 (5Gbps), but also extends link range from short-reach to long-reach using a 12-meter 26AWG cable. The S21 of such a cable is -20dB at 2.5GHz. The new receiver achieves jitter tolerance at the far-end terminal followed by such a cable is 0.76UI, with a random jitter of 0.31UI, under the BER of 10-12. This design has been fabricated in TSMC 80nm CMOS process, with the die area of 0.4mm2 for each lane.

#### **I-II-3** 11:55-12:20

A Low Power and Highly Reliable 400Mbps 512M Mobile DDR SDRAM with On-chip Distributed ECC

Saeng-Hwan Kim, Won-Oh Lee, Jung-Ho Kim, Seong-Seop Lee, Sun-Young Hwang, Chang-Il Kim, Tae-Woo Kwon, Bong-Seok Han, Sung-Kwon Cho, Dae-Hui Kim, Jae-Keun Hong, Min-Yung Lee, Sung-Wook Yin, Hyeon-Gon Kim, Jin-Hong Ahn, Yong-Tark Kim, Yo-Hwan Koh, Joong-Sik Kih(Hynix Semiconductor Inc., Korea)

**Abstract:** A 512Mb Mobile SDRAM with on-chip error correction code (ECC), which supports either single or double data rate and operates on a 1.8V power supply, is developed. The ECC circuit is optimized with respect to the increase in the chip area and the access-time penalty. The ratio of ECC area increase compared with the conventional mobile DRAM is 15%, and the fast comparing circuits of built-in Hamming code technique check 12 cell data simultaneously and satisfy the specification of 400Mbps DDR SDRAM. The self refresh period at standby state shows about 6 times increase reducing the self refresh current to be less than 100µA at 85°C. The newly adopted DCCS in the ECC, which is resistant from the clustered failures, and the concurrent row redundancy produce a synergistic fault-tolerance effect. The reliability could be 10<sup>6</sup> times higher by the ECC than that of the conventional DRAM.

#### **I-II-4** 12:20-12:45

Value Creation in SOC/MCU applications by Embedded Non-Volatile Memory Evolution Masahiro Hatanaka and Hideto Hidaka(Renesas Technology Corporation, JAPAN)]

**Abstract:** Flash-MCU, Micro-Controller with Embedded Flash Memory storage (eFlash), has seen a tremendous up-surge in real-time control application markets, with assumed 15-20% CAGR. The programmable code storage provided by eFlash contributes to production cost reduction and real-time adaptive control applications, realizing a value innovation with remarkable cost/value advantage. The diversified advanced eFlash technology for converging flash-MCU products challenges new market drivers like automotive and smart-IC cards. Current status and future directions of flash-MCU with

evolution of LSI by programmability functions are also reviewed.

## Panel Discussions November 13, 2007 (Tue.) 16:50-18:30

Panel-1 SoC or SiP: What is the Best Solution in IC Business for Ubiquitous Mobile Platforms? Organizer: Tadahiro Kuroda(Keio Univ.), Joungho Kim(KAIST) Moderator: Joungho Kim(KAIST) Panelists / position: C. Kim(Samsung) Wafer-Level 3D Chip-Stacking M. Aoyagi(AIST) Wafer-Level 3D Chip-Stacking T. Akazawa(Renesas) SiP and 3D Packaging C. H. Lee(Amkor) SiP and 3D Packaging C. P. Hung(ASE) SiP and 3D Packaging A. Lu(SIMTECH) SiP and 3D Packaging S. Y. Oh(ETRI) **Design Issues and Emerging Technologies** M. Nomura(NEC) Design Issues and Emerging Technologies T. L. Wu(NTU) **Design Issues and Emerging Technologies**

**Abstract:** Non-recurring engineering cost and development cycle for chip design and software are rapidly increasing. In addition, we are experiencing a piercing pressure for IC system packaging solutions with an extremely small form-factor. However, only a handful of big projects can pay you with the conventional approaches. Middle and small volume products may require a new solution. Could it be programmable SoC devices such as FPGA and Reconfigurable Processor, integrated with analog, RF, and memory circuits? Or, could it be SiP approach where commodity chips rather than IP's are integrated into a tiny 3D package with integrated passives and antenna? We can discuss cost, time-to-market, size, flexibility, and power consumption of these two approaches to provide the best IC system solution for ubiquitous mobile platform.

## Panel-2 Display Driver IC's: Next Technology and Market Trends

Organizer: Tadahiro Kuroda(Keio Univ.), Oh-Kyong Kwon(Hanyang Univ.)

Moderator: Oh-Kyong Kwon(Hanyang Univ.)

Panelists / position:

| 1                          |                   |

|----------------------------|-------------------|

| MH. Lee(Samsung)           | IC maker          |

| H. Hayama(NEC Electronics) | IC maker          |

| Y. Yokota(Renesas)         | IC maker          |

| Y-L Chen(Himax)            | IC maker          |

| S. Lai(Solomon Systech)    | IC maker          |

| HK. Chung, Samsung SDI     | OLED              |

| C. T. Liu(AUO)             | Panel maker (LCD) |

| T. Nishibe(TMD)            | Panel maker (LCD) |

| M. Okamoto(Sharp)          | (LCD)             |

| R. Hattori(Kyushu Univ.    | (Academia)        |

|                            |                   |

**Abstract:** The flat panel display industry has enjoyed tremendous growth over the past 15 years and has created many applications such as mobile displays, note PC's, monitors, and large-size digital TV's. The objective of this panel is to describe the technology and market trends for advances in display system and display driver IC design. In mobile display, we will discuss the technical issues on circuit integration of a-Si TFT and poly-Si TFT for low-cost and additional embedded functions such as touch screen, ambient brightness sensing and finger print recognition, and etc. and market trends among a-Si TFT-LCD, LTPS TFT-LCD and OLED. For large-size displays, we will discuss the issues of display system and chip design for 10-bit or higher-bit gray scale, optimum panel resolution(Full-HD or higher) for home TV, and how much increase the number of frame rates for higher image quality. Also, we will discuss how display and semiconductor industries make 'win-win' situation.

Session 1 Power Efficient Circuits and Systems November 13, 2007 (Tue.) 13:45-15:50

Session Co-Chairs: Hideyuki Kabuo(Panasonic), Myung H. Sunwoo(Ajou Univ.)

#### **1-1** 13:45-14:10

Performance and Power Evaluation of SH-X3 Multicore System

Masashi Takada (Hitachi Ltd., Japan), Shinichi Shibahara, Kiyoshi Hayase, Tatsuya Kamei, Yutaka Yoshida (Renesas Tech. Corp., Japan), Kiwamu Takada (Hitachi ULSI Systems Co. Ltd., Japan), Naohiko Irie (Hitachi Ltd., Japan), Osamu Nishii, and Toshihiro Hattori (Renesas Tech. Corp., Japan)

**Abstract:** We have developed an embedded processor that supports asymmetric multiple processor (AMP), symmetric multiple processor (SMP), and an AMP/SMP hybrid system. It contains four SH-X3 cores used to enhanced cache coherency from that obtained using an SH-X2 core. In this paper, we evaluate the following three techniques to improve the processing performance and reduce the power consumption in parallel processing in the processor. The first technique is snoop controller (SNC) to improve cache coherency performance. The performance overhead by snoop is decreased up to 0.1% when SPLASH-2 is executed. The second technique is detection and resolution of synonym problems so that we may not use the page coloring for page table management. The processes handling time in Linux is reduced by 29.4% compared with the case solved the problem with software. The third technique is the individual core clock frequency and the light sleep mode which is used to maintain the cache coherency even when the cores are stopped, to reduce the power consumption. The energy is decreased by 5.2% and 4.5%, respectively. As a result, the SH-X3 core achieved a performance that has a scalability proportional to 0.72-0.93 times the number of cores and a power saving of 4.5-44.0% without increasing the execution time.

#### **1-2** 14:10-14:35

Implementation of Memory-Centric NoC for 81.6 GOPS Object Recognition Processor Donghyun Kim, Kwanho Kim, Joo-Young Kim, Seungjin Lee, and Hoi-Jun Yoo (KAIST, Korea)

**Abstract:** An 81.6 GOPS object recognition processor based on Memory-Centric NoC (MC-NoC) is implemented in a 0.18um CMOS technology. The MC-NoC facilitates data transactions among 10 SIMD Processing Elements (PEs) by exploiting 8 Visual Image Processing (VIP) memories. The 10 PEs implement special SIMD instructions to perform Gaussian filtering at 16 GOPS. The 8 VIP memories provide one cycle local maximum pixels search operation performing 65.6 GOPS. The chip dissipates 1.4W at 200 MHz operating frequency.

#### **1-3** 14:35-15:00

Low hardware complexity key equation solver chip for Reed-Solomon decoders Jaehyun Baek and Myung H. Sunwoo (Ajou Univ., Korea)

**Abstract:** This paper proposes a new simplified degree computationless modified Euclid's algorithm (S-DCME) and its architecture for Reed-Solomon decoders. The proposed SDCME algorithm reformulates the existing modified Euclid's (ME) algorithm and uses new initial conditions to remove unnecessary hardware components and to use simple data paths. Thus, it requires two less multipliers

and t + 2 less multiplexers compared with the reformulated inversionless Berlekamp-Massey (RiBM) algorithm which has shown the best performance so far. The critical path delay of S-DCME is 7.92ns, i.e., TMul + TADD + TMUX, that is equal to that of RiBM. The gate count of the implemented chip using the MagnaChip HSI 0.25um standard cell library is 17,800.

#### **1-4** 15:00-15:25

An Ultra Low Power IC for a mm3-sized Autonomous Microrobot R. Casanova, A. Dieguez, A. Sanuy, A. Arbat, O. Alonso, J. Canals, and J. Samitier (Univ. of

Barcelona, Spain)

**Abstract:** This paper is focused on the main issues of designing a SoC for a completely autonomous mm3sized microrobot. It is described how all the electronics are included in a unique chip, the special requirements in the assembly process and how the hard constraints in power consumption are managed. Power in the robot is delivered by solar cells mounted on top and two supercapacitors which act as batteries. The maximum available energy for the SoC is 400uW for driving the robot actuators and 1mW for data processing. The special architecture of the SoC and power awareness are required to manage the very low available power.

#### **1-5** 15:25-15:50

Bitwise Competition Logic for Compact Digital Comparator Joo-Young Kim and Hoi-Jun Yoo (KAIST, Korea)

**Abstract:** In this paper, we present a Bitwise Competition Logic (BCL) for the high performance and area efficient digital comparator. It compares two integer numbers using the location of the first 1 from the MSB, without arithmetic computations. The detail circuits to implement BCL, pre-encoder and selection logics are explained. The implemented BCL comparator shows 16%, 38% and 30% improved result in propagation delay, transistor count, and physical area compared to the other types of comparators. Measurement waveforms of fabricated BCL comparator verify its feasibility and functionality.

Session 2 Clock & Frequency Generation November 13, 2007 (Tue.) 13:45-15:50 Session Co-Chairs: Koichiro Mashiko(STARC), Seong Hwan Cho(KAIST)

#### **2-1** 13:45-14:10

A Uniform Bandwidth PLL Using a Continuously Tunable Single-Input Dual-Path LC VCO for 5Gb/s PCI Express Gen2 Application

Woogeun Rhee, Herschel Ainspan, Daniel J. Friedman, Todd Rasmus, Stacy Garvin, and Clay Cranford (IBM, USA)

**Abstract:** A 4.75 to 6.1GHz PLL with uniform bandwidth control is implemented in 90nm CMOS. Utilizing a continuously tunable single-input dual-path LC VCO and a constant-gain phase detector, the proposed architecture is well suited to implementing PLLs that must be compliant with standards that specify minimum and maximum allowable PLL bandwidths such as PCI Express Gen2 or FB-DIMM applications. This work also addresses noise and coupling aspects in dual-path VCO design. The

measurement results show that the PLL bandwidth and random jitter (RJ) variations are well regulated and that the use of a differentially controlled dual-path VCO is important for deterministic jitter (DJ) performance.

#### **2-2** 14:10-14:35

A 480-MHz to 1-GHz Sub-picosecond Clock Generator with a Fast and Accurate Automatic Frequency Calibration in  $0.13\text{-}\mu\text{m}$  CMOS

Joonhee Lee (KAIST, Korea), Kyunglok Kim (Stanford Univ., USA), Junghyup Lee, Taekwang Jang, and Seonghwan Cho (KAIST, Korea)

**Abstract:** In this paper, an ultra-low jitter clock generator that employs a novel automatic frequency calibration (AFC) technique is presented. To achieve low jitter, the clock generator uses an LC-VCO with 5-bit switched tuning scheme. The clock output is taken from the output of a multi-modulus divider, which increases the output frequency range with small variation in the loop bandwidth. The capacitor array of the the VCO is controlled by a novel AFC technique that performs binary search for fast calibration and fine search to select an optimum tuning curve. A prototype chip implemented in 0.13um CMOS process achieves 480 MHz to 1GHz of output frequency while consuming 22mW from a 1.2V supply. The measured rms jitter and calibration time of the proposed clock generator are 940fs at 600MHz and 350ns, respectively. These numbers are the fastest calibration time and one of the lowest jitter that have been reported in a clock generator.

#### **2-3** 14:35-15:00

Bi-directional AC Coupled Interface with Adaptive Spread Spectrum Clock Generator Yoshihide Komatsu, Tsuyoshi Ebuchi, Takashi Hirata, and Takefumi Yoshikawa (Matsushita Electric Industrial, Japan)

**Abstract:** We propose a method of reducing a quantization noise and a spectrum peak utilizing an adaptive spread spectrum clocking PLL (SSC-PLL) circuit for Bi-directional and AC coupled interface. To realize a high speed, wide range, bi-directional and long cable transceiver, we designed a test chip that contained an Equalizer, CDR, and differential transceiver for long cable, and also an SSC-PLL for reducing spectrum peak with jitter optimization by adaptive bandwidth setting. Utilize this interface, it can be realized up to 810Mbps and 20m bi-directional transceiver system with high ESD protection, and spectrum peak reduction about -23dB effectively with an optimum bandwidth calibration.

#### **2-4** 15:00-15:25

A 3-10 GHz Full-Band Single VCO Agile Switching Frequency Generator for MB-OFDM UWB Chao-Shiun Wang, Wei-Chang Li, Chorng-Kuang Wang (Nat'l Taiwan Univ., Taiwan), Horng-Yuan Shih (Nat'l Chiao Tung Univ., Taiwan), and Tzu-Yi Yang (Industrial Tech. Research Inst., Taiwan)

**Abstract:** This paper presents an agile switching frequency generator with a single voltage controlled oscillator (VCO) covering all the 14 bands for MB-OFDM UWB system. The proposed architecture with the group selection mixers is designed to simplify the synthesizer implementation for optimizing the system power consumption and harmonic sideband spurious suppression. This frequency generator, which consists of a series of dividers, quadrature counterbalance single sideband mixers and output buffers, achieves an agile switching time of 7ns and the unwanted sidebands of less than 35dBc. The

circuit occupies an active area of 1.8x1.6mm2 in a 0.13um mixed mode CMOS technology. The overall system draws a current consumption of 49mA from a 1.2V supply.

#### **2-5** 15:25-15:37

A 6.1-mW Dual-Loop Digital DLL with 4.6-ps RMS Jitter using Window-Based Phase Detector Paritosh Bhoraskar and Yun Chiu (UIUC, USA)

**Abstract:** A 0.13um CMOS dual-loop digital DLL for multiphase clock generation and synchronization is presented. Ten clock phases are produced and locked to a first reference clock by the inner loop, while the outer loop further aligns all phases simultaneously to a second reference clock at a higher frequency. Unlike usual dual-loop DLLs, the proposed architecture has one loop completely enclosed inside the other, resulting in a secondorder behavior. A window-based phase detection technique is exploited to minimize the circuit complexity and power with uncompromised jitter performance. The false-lock-free DLL operates over a wide frequency range of 0.2-1.2 GHz, measures a 4.6ps rms jitter, and consumes 6.1mW at 1.2GHz.

#### **2-6** 15:38-15:50

A 7mA-1.8V, 2MHz GFSK Analog Demodulator with 1Mbps Data Rate Jinke Yao, Baoyong Chi, Zhihua Wang (Tsinghua Univ., China)

**Abstract:** A 7mA-1.8V, 2MHz GFSK analog demodulator with 1Mbps data rate for the short-distance wireless communication systems is presented. The demodulator includes a 5-order Butterworth pre-filter with 4MHz bandwidth, a 7-stage limiter, a quadrature frequency discriminator with 4-order Bessel phaseshift network, a 4-order Butterworth post-filter with 800kHz bandwidth and a differentiator-based bit discriminator. Three filters share a same PLL-based automatic tuning network to lower down the power consumption. The system optimization is carried out to select the coupling scheme between various blocks, the gain assign scheme, the bandwidth plan, as well as the order of the Bessel low pass network as the 90 degree phase shifter. All the blocks are designed with the target of low power, high carrier frequency offset and high data rate at the 1.8V power supply. The GFSK analog demodulator has been implemented in 0.18um CMOS. The measured results show that the demodulator could directly restore the digital data from a 2MHz GFSK signals with 1Mbps data rate and ±160KHz maximum frequency deviation. The analog demodulator has a sensitivity of -53dBm, and could undertake a high carrier frequency offset (from 1.3MHz to 2.7MHz). It draws 7mA current from a power supply of 1.8V.

### Session 3 High Performance Amplifiers and Varactor-Less VCO November 13, 2007 (Tue.) 13:45-15:50

Session Co-Chairs: Chien-Nan Kuo(Nat'l Chao Tung Univ.), Byung-Sung Kim(SungKyunKwan Univ.)

#### **3-1** 13:45-14:10

A Linearization Technique for RF Receiver Front-End Using Second-Order-Intermodulation Injection Shuzuo Lou and Howard C. Luong (Hong Kong Univ. of Science & Tech., Hong Kong)

**Abstract:** A linearization technique is proposed in which lowfrequency 2nd-order intermodulation IM2 is injected to suppress the 3rd-order intermodulation IM3. The proposed linearization technique is applied to both an LNA and a down-conversion mixer in an RF receiver front-end (RFE) working at 900MHz. Fabricated in a 0.18um CMOS process and operated at 1.5 V supply, the RFE delivers 22dB gain with 5.3dB noise figure (NF). The linearization technique measures around 20-dB IM3 suppression without gain reduction and noise penalty, and with only extra current of 0.2 mA.

#### **3-2** 14:10-14:35

A CMOS Wide-Band Low-Noise Amplifier With Balun-Based Noise-Canceling Technique Youchun Liao, Zhangwen Tang, and Hao Min (Fudan Univ., China)

**Abstract:** A differential high linearity low-noise amplifier (LNA) based on a capacitor-cross-coupled topology is presented in this paper. An off-chip balun is used for providing DC-bias and canceling the channel thermal noise of the transconductance MOS transistor. The LNA uses NMOS load and provides an extra signal feed-forward and noise-canceling path. Analysis shows that the noise contribution of the transconductance MOST is only gamma/20 and the noise figure (NF) of the proposed LNA is 1+0.2gamma. The chip is implemented in a 0.18um MMRF CMOS process. Measured results show that in 50M-860MHz frequency range, the LNA achieved 15dB gain, 2.5dB NF, 8.3dBm IIP3 and consumes only 4mA current from a 1.8V supply.

#### **3-3** 14:35-15:00

A Low-Power, 3-5-GHz CMOS UWB LNA Using Transformer Matching Technique Dong Hun Shin (UCSB, USA), Jaejin Park (Samsung Electronics, Korea), and C. Patrick Yue (UCSB, USA)

**Abstract:** This paper presents the design of a 3–5GHz CMOS ultra-wideband (UWB) low-noise amplifier (LNA) utilizing an on-chip transformer to achieve low-power operation and to realize a compact input matching network. Detailed analyses of the input match, voltage gain, and noise figure of the LNA are provided. Implemented in 0.13um CMOS, the LNA achieves a maximum power gain of 16.2 dB, an input return loss of greater than 11.0 dB, and a minimum noise figure of 2.8 dB for the 3–5-GHz UWB while consuming only 6.7 mW from a 1.2-V supply. The active area of the fabricated CMOS UWB LNA is 0.32 mm2.

#### **3-4** 15:00-15:12

A 1.5dB NF, 5.8GHz CMOS Low-Noise Amplifier with On-Chip Matching J. S. Duster, S. S. Taylor (Intel Corp., USA), and J. H. C. Zhan (MediaTek Inc., Taiwan) **Abstract:** In this paper we describe the design of an integrated 5.8GHz low noise amplifier in 90nm CMOS technology. The design is a tuned cascode LNA with on-chip matching that has a sufficiently low noise figure and high gain to enable high receiver sensitivity. The measured performance is NF=1.5dB, gain=28 dB, IIP3=-5dBm and Pd=15mW; and NF=1.8dB, gain=23dB, IIP3=-17dBm and Pd=8mW

#### **3-5** 15:13-15:25

A CMOS Linear-in-dB High-Linearity Variable- Gain Amplifier for UWB Receivers Chan Tat Fu and Howard Luong (The Hong Kong Univ. of Science and Tech., Hong Kong)

**Abstract:** This paper presents a CMOS linear-in-dB variable gain amplifier (VGA) that provides a variable gain range over 90dB with 3dB bandwidth greater than 400MHz at 54dB gain. The maximum output 1dB compression point is 9dBm. Maximum gain error is +/-2dB. It consumes total 22mW with 1.8V supply, including control circuit. This VGA is fabricated in TSMC 0.18um CMOS process and demonstrate the performance of the proposed dB-linear VGA.

#### **3-6** 15:25-15:37

A 0.18-µM CMOS 16-GHZ Varactorless LC-VCO with 1.2-GHZ Tuning Range Chih-Hsiang Chang and Ching-Yuan Yang (Nat'l Chung-Hsing Univ., Taiwan)

**Abstract:** The paper describes a 16GHz monolithic varactorless LC-tank VCO implemented in a 0.18um CMOS technology. Unlike the traditional tuning method by a varactor, in this work a tunable inductor, which is introduced by a transformer based on tuning currents from the active components controlled by the input voltage, is employed in the VCO. Without a varactor in the LC tank, the oscillator can easily arrive at the requirement for high-frequency operation. The VCO using a symmetry transformer provides the tuning range of 15.44 to 16.64GHz (7.5%) at 1.8 V supply. With operating at 16GHz frequency, the measured phase noise is -118.6 dBc/Hz at 1MHz offset, and the VCO dissipates around 3.3mA.

#### **3-7** 15:38-15:50

A 2.5-3.2GHz GH3 Continuously-Tuned Varactor-Less LC-VCO with Differential Control Deyi Pi, Byung-Kwan Chun, and Payam Heydari (Univ. of California, Irvine, USA)

**Abstract:** The design and implementation of a 2.5-3.2GHz LC-VCO incorporating a varactor-less tuning technique is presented. The VCO's oscillation frequency is tuned differentially by varying the effective inductance of the oscillators. Fabricated in a 0.18um CMOS process, the prototype VCO achieves 24% continuous tuning range without varactors. The circuit draws 7-15mA current from a 1.8V power supply. The measured phase noise is varying between -102dBc/Hz and -111dBc/Hz at 1MHz offset across the tuning range.

## Session 4 Emerging Trends in Proximity Interface

November 13, 2007 (Tue.) 13:45-15:50

Session Co-Chairs: C. Patrick Yue(UC Santa Barbara), Koji Kotani(Tohoku Univ.)

#### **4-1** 13:45-14:10

Non-Contact 10% Efficient 36mW Power Delivery Using On-Chip Inductor in 0.18-µm CMOS Yuan Yuxiang, Yoichi Yoshida, and Tadahiro Kuroda (Keio Univ., Japan)

**Abstract:** This paper presents design and implementation of an inductive coupling power delivery system between stacked chips in 0.18um CMOS process. Two conventional high-power rectifier structures are compared, and a new topology is proposed. Several low-power circuit design techniques are employed to improve the power conversion efficiency and high frequency performance of the rectifier block. With a pair of fully optimized 700um x 700um on-chip inductors, the test chip achieves 10% peak efficiency and 36mW power transmission. Compared with previous published chip-to-chip wireless power transmission systems, the received power is 13 times larger.

#### **4-2** 14:10-14:35

High Efficiency CMOS Rectifier Circuit with Self-Vth-Cancellation and Power Regulation Functions for UHF RFIDs

Koji Kotani and Takashi Ito (Tohoku Univ., Japan)

**Abstract:** High efficiency CMOS rectifier circuit for UHF RFID applications has been developed. The rectifier utilizes self Vth cancellation (SVC) scheme in which threshold voltage of MOSFETs is cancelled by applying gate bias voltage generated by output voltage of the rectifier itself. Very simple circuit configuration and no power dissipation feature of the scheme enable excellent power conversion efficiency (PCE) especially in small RF input power conditions. At higher RF input power conditions, PCE of the rectifier automatically decreases. This is the built-in self-power-regulation function the rectifier has. Proposed SVC CMOS rectifier has been fabricated with 0.35um CMOS process and the measured performance has been compared with other types of rectifiers. The SVC CMOS rectifier achieves 29% PCE at -9.9dBm RF input power condition. This PCE is larger than ever reported rectifiers under the condition.

#### **4-3** 14:35-15:00

A Fully Integrated Wireless Power Supply for Pinless Active RFID-devices in 130nm CMOS Christophe De Roover and Michiel Steyaert (Katholieke Universiteit Leuven, Belgium)

**Abstract:** This paper presents the first fully integrated and pinless wireless 0.5V-power supply for RFID applications in 130nm CMOS. It consists of an on-chip integrated dipoleantenna, a rectifier and storage capacitor. The system can generate 0.5V from 36.4dBmEIRP at a distance of 0.5m, the operating frequency being 10.35GHz +- 1%. The integrated antenna is a dipole with a reflector underneath, to shield it from the lossy substrate. The rectifier uses a 20-stage voltage-doubler topology to rectify the incoming power. The die area is only 300um x 1500um.

#### **4-4** 15:00-15:25

A 2Gb/s Bi-Directional Inter-Chip Data Transceiver with Differential Inductors for High Density

Inductive Channel Array

Yoichi Yoshida, Noriyuki Miura, and Tadahiro Kuroda (Keio Univ., Japan)

**Abstract:** A 2Gb/s bi-directional inter-chip data transceiver is experimentally demonstrated for the first time in 180nm CMOS technology. Two orthogonal differential inductor pairs are vertically overlapped to make a bi-directional channel. Using these channels, bi-directional communication system is established without any complex circuit techniques. The crosstalk interference problem in channel array is also considered. Noise immunity of differential inductors can make shorter pitch possible in channel array. Compare with data link with conventional inductor array, this proposal technique achieves 2 times higher channel-density with the same speed.

#### **4-5** 15:25-15:37

Interference from Power/Signal Lines and to SRAM Circuits in 65nm CMOS Inductive-Coupling Link Kiichi Niitsu (Keio Univ., Japan), Kenichi Osada, Naohiko Irie (Hitachi, Japan), Hiroki Ishikuro, and Tadahiro Kuroda (Keio Univ., Japan)

**Abstract:** This paper discusses interference of an inductivecoupling link in 65nm CMOS. Electromagnetic interference from power/signal lines and to SRAM was simulated and measured. Interference from power lines for mobile applications (line and space) is smaller than that for highperformance applications (mesh type). Interference from signal lines requires only 9% of additional transmit power even in the worst case of logic circuits. In typical operation range, interference to SRAM is ignorable. Only when supply voltage is much lower than typical range, the bit-line noise from the inductive-coupling link influences SRAM operation. Interference to SRAM is small compared with other influences such as device variations and soft errors.

#### **4-6** 15:38-15:50

An EPC Gen 2 Compatible Passive/semi-active UHF RFID Transponder with Embedded FeRAM and Temperature Sensor.

Shiho Kim, Jung-Hyun Cho, Hyun-Sik Kim, Haksu Kim (Chungbuk Nat'l Univ., Korea), Hee-Bok Kang, and Suk-Kyung Hong (Hynix Semiconductor, Korea)

**Abstract:** A fully integrated passive and battery powered semi-active UHF RFID transponder chip supporting EPC Gen 2 protocol is presented. The proposed transponder works as a passive RFID tag when the generated RFpower is sufficient to operate, otherwise it operates in semi-active mode using battery power. The chip has rewriteable non-volatile memory bank formed by FeRAM and on-chip temperature sensor. The memory consists of EPC memory bank for EPC functionality and temperature bank for storing sensed data. The standby current in semiactive is about 0.5uA, the lifetime in semi-active mode is in excess of 2 year with a 10mA-hr thin film battery.

#### Session 5 Wireless & Wireline Communication November 14, 2007 (Tue.) 11:05-13:10

Session Co-Chairs: Tszshing Cheung(Fujitsu), Joonbae Park(GCT Semiconductor)

**5-1** 11:05-11:30

A 180-Mb/s to 3.2-Gb/s, Continous-Rate, Fast-Locking CDR without Using External Reference Clock Moon-Sang Hwang, Sang-Yoon Lee, Jeong-Kyoum Kim, Suhwan Kim, and Deog-Kyoon Jeong (Seoul Nat'l Univ., Korea)

**Abstract:** A referenceless, continuous-rate, fast-locking CDR with an operating range of 180 Mb/s to 3.2 Gb/s is presented. The harmonic lock property of a rotational frequency detector and the maximum run-length limit of 8B10B encoded data are utilized to detect a harmonic lock and to accelerate acquisition process. A separate VCO control scheme is introduced to stabilize the loop with a modest amount of on-chip capacitance.

#### **5-2** 11:30-11:55

A 26.5-37.5 GHz Frequency Divider and a 73-GHz-BW CML Buffer in 0.13 μm CMOS Jeong-Kyoum Kim, Jaeha Kim, Sang-Yoon Lee, Suhwan Kim, and Deog-Kyoon Jeong (Seoul Nat'l Univ., Korea)

**Abstract:** This paper presents a frequency divider with a wide operating frequency range and a high bandwidth CML buffer intended for an 80Gb/s serial link system. The proposed divider uses a pulsed-latch architecture that replaces the slave latch in a flip-flop-based divider with a buffer. The CML buffer employs both shunt-and-double-series inductive peaking and active feedback. Implemented in a 0.13um CMOS process with fT of only 82 GHz, the divider operates over a wide range of 26.5-37.5 GHz with an input sensitivity of 1 Vpp, diff and produces a nominal output swing of 1 Vpp, diff. The CML buffer achieves a -3dB bandwidth of 73.5 GHz in simulation, which is high enough to buffer an 80Gb/s NRZ data stream. The fabricated frequency divider and clock buffers dissipate 22.5 mW and 72 mW, respectively, from a 1.8V supply.

**5-3** 11:55-12:07

A Quad 1-10Gb/s Serial Transceiver in 90nm CMOS

Han Bi, Yehui Sun, Kai Lei, Zixin Wu, Xinqing Chen, Song Gao, Junning Wang, Yongyi Wu, and Hui Wang (IDT, China)

**Abstract:** A quad 1-10Gb/s serial transceiver in 90nm digital CMOS technology is presented in this paper. A combination of transmitter pre-emphasis and receiver equalization is used. It can be used for different data rates and short-reach/long-reach applications with low overhead in area and power consumption. It is able to run across a 60-inch FR4 PCB trace with BER<10-12 at 3.125Gb/s while consuming 70mW/channel. At 10Gb/s, it consumes 98mW/channel to run across a 10-inch FR4 PCB trace and 90mW/channel to run across a 4-inch FR4 PCB trace. Its die area is 1.6mm2.

**5-4** 12:08-12:20

A 2.5Gb/s ESD-Protected Dual-Channel Optical Transceiver Array Jungwon Han, Booyoung Choi (Ewha Womans Univ., Korea), Kangyeob Park, Won Seok Oh (KETI, **Abstract:** This paper describes the design of a dual-channel optical transceiver array realized in a standard 0.18um CMOS technology for the applications of high-speed digital interface. The transmitter drives a 2-channel VCSEL array at 2.5Gb/s, equipped with the APC (5-15mA) and AMC (4-20mApp) loops for constant and reliable optical power outputs. Meanwhile, the receiver exploits the common-gate transimpedance amplifier, demonstrating 87dBOhm transimpedance gain, 1.4GHz bandwidth for 2pF input parasitic capacitance, -18dBm sensitivity for 10-12 BER, and less than -20dB crosstalk between TX and RX within the bandwidth. The whole 2-channel transceiver array chip dissipates 500mW.

#### **5-5** 12:20-12:32

A Low-Power Current-Mode Transceiver with Simultaneous Data and Clock Transmission at 625Mb/s, 3 mW in 1.5 V for Mobile Applications

Tetsuhiro Ogino (Kobe Univ., Japan), Takefumi Yoshikawa (Matsushita Electric Industrial Co., Ltd., Japan), and Makoto Nagata (Kobe Univ., Japan)

**Abstract:** A current-mode data transceiver for mobile applications is described. This transceiver has a multi-level current transmitter with simple clock recovery and a low-input impedance receiver, and realizes low-voltage swing (about 20mV) with 150-300uA drive current at 625 Mbps by differential manner. The transceiver operates with a 1.5V single power supply, and consumes 3 mW including transmitter and receiver when simultaneous data and clock transmission at 625Mbps is achieved through a single differential I/O connecting the transmitter and receiver pair.

#### **5-6** 12:33-12:45

A Fully Integrated 2.4GHz Low IF CMOS Transceiver for 802.15.4 ZigBee Applications Yun Seong Eo, Hyun Jin Ryu (Kwangwoon Univ., Korea), Seong-Sik Song (KAIST, Korea), Young Joon Ko, and Jae Young Kim (ETRI, Korea)

**Abstract:** A fully integrated 2.4 GHz RF transceiver compliant with the low-power ZigBee (IEEE 802.15.4) standard is presented. The RF transceiver adopts low IF receiver and direct up-conversion transmitter. It consumes 18mA in receive mode and 17mA in transmit mode with 1.8-V power supply. The receiver chain IIP3 is -13.5 dBm and BBA poly phase filter can reject the ACI/AACI interferers. The achieved transmitter's maximum power is 4.7dBm and its EVM is 8.4% at 0.5dBm output. The LO generation is achieved using frequency mixing method and thus it can prevent the VCO pulling. The die area is 2.5 mm x 2.6 mm.

#### **5-7** 12:45-12:57

A Low Power CMOS Transceiver for 915 MHz-Band IEEE 802.15.4 Standard T.-K. Nguyen, V.-H. Le, Q.-H. Duong, S.-K. Han, S.-G. Lee (ICU, Korea), N.-S. Seong, and N.-S. Kim (ETRI, Korea)

**Abstract:** This paper reports a low power and low cost transceiver for 915 MHz-band IEEE 802.15.4b standard. Low power and low cost design are persured by optimizing transceiver architecture and circuit topology. The proposed transceiver shares analog baseband for both receiver and transmitter saving a silicon area. The transceiver consumes 11.2 mA and 22.5 mA for receive and transmit mode from 1.8 V

supply including 5 mA of VCO and frequency divider currents. The proposed transceiver is implemented in a 0.18um CMOS process and occupies 10 mm2 of silicon area.

#### **5-8** 12:58-13:10

An NFC Transceiver with RF-powered RFID Transponder Mode Jung-Hyun Cho, Jikon Kim, Jae-Whan Kim, Kyungil Lee, Kwang-Duk Ahn, and Shiho Kim (Chungbuk nat'l Univ., Korea)

**Abstract:** A single chip NFC transceiver supporting not only NFC active and passive mode but also 13.56MHz RFID reader and tag mode was designed and fabricated. The proposed NFC transceiver can operate as a RFID tag even without external power supply thanks to a dual antenna structure for initiator and target. The area increment due to additional target antenna is negligible because the target antenna is constructed by using a shielding layer of initiator antenna.

#### Session 6 Multimedia Signal Processing

November 14, 2007 (Tue.) 11:05-13:10 Session Co-Chairs: *Hideyuki Noda(Renesas), Ramchan Woo(LG Electronics)*

#### **6-1** 11:05-11:30

A Low Power and High Picture Quality H.264/MPEG-4 Video Codec IP for HD Mobile Applications Seiji Mochizuki, Tetsuya Shibayama, Masaru Hase, Fumitaka Izuhara, Kazushi Akie, Masaki Nobori, Ren Imaoka, Hiroshi Ueda, Kazuyuki Ishikawa, and Hiromi Watanabe (Renesas Tech. Corp., Japan)

**Abstract:** We have developed an H.264/MPEG-4 video codec IP for mobile applications such as digital still cameras (DSCs) and digital video cameras (DVCs). The codec is capable of encoding/decoding HD sized moving pictures (1280 pixels by 720 lines at 30 fps) in real-time at an operating frequency of 144 MHz, and SD sized at 54 MHz. The original algorithms employed in the codec realize low power of 64 mW for encoding HD with high picture quality equivalent to JM reference encoder.

#### **6-2** 11:30-11:55

A Multi Matrix-processor Core Architecture for Real-time Image Processing SoC Katsuya Mizumoto, Tetsushi Tanizaki, Soichi Kobayashi, Masami Nakajima, Takayuki Gyohten, Hiroyuki Yamasaki, Hideyuki Noda, Motoki Higashida, Yoshihiro Okuno, and Kazutami Arimoto (Renesas Tech. Corp., Japan)

**Abstract:** This paper describes a real time image processing SoC(MX-SoC) with programmable multi matrix -processor(MX-Core) architecture. The MX-SoC has three MX-Cores, Host-CPU, and I/O peripheral modules. An unit MX-Core is a massively parallel (1024) flexible SIMD processor based on the matrix architecture. The MX-SoC, which can perform the image processing of CCD camera, is implemented on 90nm Low Power CMOS process technology and can operate at 162MHz under the worst condition. A novel parallel pixel data processing algorism, and multi task execution suitable for multi MX-Core processing can achieve 30 Frame/sec image processing. This performance is 30 times faster than general purpose CPU solution. The MX-SoC with multi MX-Core architecture can realize the

software solution of real time image processing application field.

#### **6-3** 11:55-12:20

A Novel Compression Method for Wireless Image Sensor Node Xinkai Chen, Hanjun Jiang, XiaoWen Li, and Zhihua Wang (Tsinghua Univ., China)

**Abstract:** This paper presents the design of a novel compression method for wireless image sensor node. In order to meet the requirement of the wireless image sensor node, a dedicated filtering procedure is developed for raw Bayer CFA pattern. JPEG-LS encoder follows the filtering procedure to compress the data. The parallel and pipeline structure are chosen for the purpose of high throughput and real-time operation. The compression method is implemented using UMC 0.18um technology. The test results shown that the image with VGA (640x480) resolution and frame rate 15 fps can be achieved with the same clock frequency with the CMOS image sensor.

#### **6-4** 12:20-12:32

A VGA 30-fps Optical-Flow Processor Core Based on Pyramidal Lucas and Kanade Algorithm Hajime Ishihara, Masayuki Miyama, Yoshio Matsuda (Kanazawa Univ., Japan), Yuichiro Murachi, Yuki Fukuyama, Ryo Yamamoto, Junichi Miyakoshi, Hiroshi Kawaguchi, and Masahiko Yoshimoto (Kobe Univ., Japan)

**Abstract:** This paper describes an optical-flow processor core for real-time video recognition. The processor is based on the Pyramidal Lucas and Kanade algorithm. It has small chip area, a high pixel rate, and high accuracy compared to conventional optical-flow processors. Introduction of search range limitation and the Carman filter to the original algorithm improves the optical-flow accuracy and reduces the processor hardware cost. Furthermore, window interleaving and window overlap methods can reduce the necessary clock frequency of the processor by 70%. The proposed processor can handle a VGA 30fps image sequence with 332MHz clock frequency. The core size and power consumption in 90nm process technology are estimated respectively as 3.50 x 3.00 mm2 and 600mW.

#### **6-5** 12:33-12:45

1.8mW, Hybrid-Pipelined H.264/AVC Decoder For Mobile Devices Sangkwon Na, Woong Hwangbo, Jaemoon Kim, Seunghan Lee, and Chong-Min Kyung (KAIST, Korea)

**Abstract:** H.264/AVC has brought a drastic quality improvement of videos, but requires unprecedented computing power. To meet performance, area and power constraints, we propose a hybrid pipeline architecture, and a data reuse mechanism to reduce off-chip memory access. Fully 4x4 sub-macroblock pipeline architecture is optimized for low power as well as performance. The proposed H.264/AVC decoder architecture can support CIF(352x288) 30fps videos at 6MHz with 1.8mW @1.65V, implemented in 0.18um technology.

#### **6-6** 12:45-12:57

A Novel Design of CAVLC Decoder with Low Power Consideration Tsung-Han Tsai and De-Lung Fang (Nat'l Central Univ., Taiwan) **Abstract:** This paper proposes a novel architecture and its VLSI design for MPEG-4 AVC/H.264 CAVLC decoding. In order to improve throughput of CAVLC decoder, we propose two new methods, which are called MLD (Multi-Level Decoding) and NZS (Non Zero Skip for run\_before decoding). By performing parallel operation on level decoder, MLD can decode two levels in one cycle at most situations, and NZS can produce several run\_befores in the same cycle. These two methods have the advantages of low complexity and regularity design. According to the evaluation, our design only needs 137 cycles in average for one macroblock decoding. Moreover, the proposed CAVLC decoder can run at 33.5 MHz to meet the real time requirement for H.264 video decoding on  $1920 \times 1088$  resolution. Compared with the previous designs, it can reduce around 29.1% to 71.5% on operation frequency for the same requirement, but not increase the gate count so much. With an aid on a lower operation frequency, it will be suitable for a low power application.

#### **6-7** 12:58-13:10

An SoC Based HW/SW Co-Design Architecture for Multi-Standard Audio Decoding Dajiang Zhou, Peilin Liu, Ji Kong, Yunfei Zhang, and Bin He (Shanghai Jiaotong Univ., China)