# ADVANCE PROGRAM

# 2002 IEEE INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

FEBRUARY 3, 4, 5, 6, 7

CONFERENCE THEME: ICs FOR INFORMATION TECHNOLOGIES

> SAN FRANCISCO MARRIOTT HOTEL

VEB REGISTRATION: Hotel. Conference: 1 Short Course. 7 Tutorials. 2 Workshops 2 SPECIAL EVENING SESSIONS: Inductance (for Digital); Low-Power Design 1 WORKSHOP: Telecom Access Circuits; 7 TUTORIAL SUNDAY ALL-DAY:

> 5-DAY PROGRAM

#### ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-ona-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and use to maintain technical currency, and to network with leading experts.

#### CONFERENCE HIGHLIGHTS

On Sunday, February 3<sup>rd</sup>, the day before the official opening of the Conference, ISSCC 2002 offers a choice of up to 3 of a total of 7 Tutorials. The SSCTC Workshop on *Analog Telecom Access Circuits and Concepts* is also offered during the day on Sunday. New for 2002, two special-topics evening sessions addressing next-generation circuit design challenges will be offered on Sunday starting at 7:30PM: *Inductance: Implications and Solutions for High-Speed Digital Circuits,* and *Low-Voltage Design for Portable Systems.* These sessions offer leading experts in the field presenting tutorial background and state-of-the-art design strategies in a workshop format and are open to all ISSCC attendees.

On Monday, February 4<sup>th</sup>, ISSCC 2002 offers three plenary papers followed by five parallel sessions of technical papers. There will be a Social Hour for all registrants from 5:00PM to 6:30PM in the Golden Gate Hall (on the level above the Ballroom). Evening panel discussions will be held on Monday and on Tuesday evenings from 8:00PM to 10:00PM. Technical sessions continue on Tuesday and Wednesday.

On Thursday, February 7<sup>th</sup>, ISSCC 2002 offers an ISSCC Microprocessor Design Workshop on *High-Frequency Clocking: Issues and Solutions for Clocking High-Frequency Microprocessors*. The ISSCC Short Course on *Wideband Communications* will also be held on Thursday. Three sessions of the Short Course will be offered with staggered starting times; these will be filled on a first-come, first-served basis.

Use of the ISSCC web-registration site is strongly encouraged. You will be provided with immediate confirmation on registration for Tutorials, SSCTC Workshop, ISSCC Workshop and ISSCC Short Course if you use web registration either through the link on the ISSCC website (www.isscc.org) or directly to the ISSCC registration site (www.seminarsource.com/isscc2002).

#### CONFERENCE INFORMATION

The **timing of papers permits session-hopping** without missing important material. This Program gives you the starting time for each paper. Taking of **pictures and videos** during sessions is **not permitted**. A printed supplement with speakers' visuals will be sent to all registered attendees within one month of the conclusion of ISSCC 2002.

A CDROM containing both the ISSCC 2002 Digest of Technical Papers and the Visuals Supplement will be mailed in late Spring to speakers and all attendees paying the member or non-member Conference registration fee.

**Conference Information:** Courtesy Associates, Fax: 202-973-8722; email: <u>isscc@courtesyassoc.com</u>.

Press Information: Kenneth C. Smith, University of Toronto, Phone: 416-978-5033; Fax: 416-971-2286; email: <u>lcfujino@cs.com</u>

Registration: SeminarSource, FAX: 1-619-293-7332 or 1-619-293-0793; Telephone: 1-619-293-0684 or 1-888-288-1827.

**Sponsorship:** ISSCC 2002 is sponsored by the IEEE Solid-State Circuits Society. Co-sponsors are the IEEE San Francisco Section and Bay Area Council, and the University of Pennsylvania.

Website: See http://www.isscc.org

## CONTENTS

| SS                               | orials<br>CTC Workshop<br>ecial Topic Evening Session: Inductance, and                            | 8       |  |

|----------------------------------|---------------------------------------------------------------------------------------------------|---------|--|

| Spe                              | Solutions for High-Speed Digital Circuits<br>ecial Topic Evening Session: Low -Voltage Design for |         |  |

|                                  | Portable Systems                                                                                  | 11      |  |

|                                  | PAPER SESSIONS                                                                                    |         |  |

| 1                                | Plenary Session                                                                                   | 12      |  |

| 2                                | Image Sensors                                                                                     |         |  |

| 3                                | Digital Signal Processors, Circuits, and Systems                                                  | 16      |  |

| 4                                | Backplane Interconnects and Clock Multipliers                                                     |         |  |

| 5                                | Wireless-Networking Transceivers                                                                  |         |  |

| 6                                | Non-Volatile Memories and SRAM                                                                    |         |  |

|                                  | DISCUSSION SESSIONS                                                                               |         |  |

| F1                               | Software Radio: Cool or to be Cooled?                                                             | 24      |  |

| E2                               | When Will Optical Interconnects Appear on High-                                                   |         |  |

|                                  | Performance Microprocessors?                                                                      | 24      |  |

| F3                               | Does Moore's Law Apply to Analog?: Past, Present, and                                             |         |  |

| -0                               | Future Implications of Technology Progress and                                                    |         |  |

|                                  | Higher Levels of Integration for Mixed-Signal Circuits                                            | 25      |  |

| F4                               | Have Universities Killed Research - or Has Industry                                               | 20      |  |

|                                  | Corrupted It?                                                                                     | 25      |  |

|                                  | PAPER SESSIONS                                                                                    |         |  |

| 7                                | Baseband Communications                                                                           | 26      |  |

| 8                                | High-Speed Timing                                                                                 |         |  |

| 9                                | DRAM and FerroElectric Memories                                                                   |         |  |

|                                  | High-Speed Analog-to-Digital Converters                                                           | 32      |  |

| 11                               | TD: RF/High-Speed Technologies                                                                    | 34      |  |

| 12                               | TD: Digital Directions                                                                            | 36      |  |

| 13                               | Oversampling A/D Converters                                                                       | 38      |  |

| 14                               | Cellular RF Wireless                                                                              | 40      |  |

|                                  | nference Timetable                                                                                |         |  |

| Reg                              | gistration and Reservation Forms                                                                  | Inserts |  |

|                                  | Gigabit Communications                                                                            |         |  |

|                                  | High-Speed Circuit Techniques and I/O                                                             |         |  |

|                                  | DISCUSSION SESSIONS                                                                               |         |  |

| E5                               | Low-Voltage Design or the End of MOSFET Scaling?                                                  | 48      |  |

| E6                               | SOI: Solution or Indigestion?                                                                     | 48      |  |

|                                  | What Caused The Telecom Crash: Technology,                                                        |         |  |

|                                  | Business or Demand?                                                                               | 49      |  |

| E8                               | Solid-State Circuits: System or Circuit Innovation?                                               | 49      |  |

|                                  | PAPER SESSIONS                                                                                    |         |  |

|                                  | Advanced RF Techniques                                                                            |         |  |

| 18                               | Converter Techniques                                                                              | 52      |  |

|                                  | DSL and Wireline Circuits                                                                         |         |  |

| 20                               | Microprocessors                                                                                   | 56      |  |

| 21                               | TD: Sensors and Microsystems                                                                      | 58      |  |

| 22                               | Multimedia Signal Processing                                                                      | 60      |  |

|                                  | Analog Techniques                                                                                 |         |  |

| 24                               | RF Systems                                                                                        | 64      |  |

|                                  | Processor Building Blocks                                                                         |         |  |

| 26                               | MEMS and Displays                                                                                 | 68      |  |

| Sho                              | ort Course: Wideband Communications                                                               | 70      |  |

| Microprocessor Design Workshop72 |                                                                                                   |         |  |

|                                  | ormation                                                                                          |         |  |

|                                  | mmittees                                                                                          |         |  |

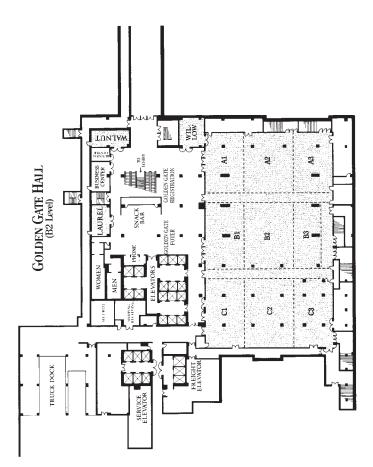

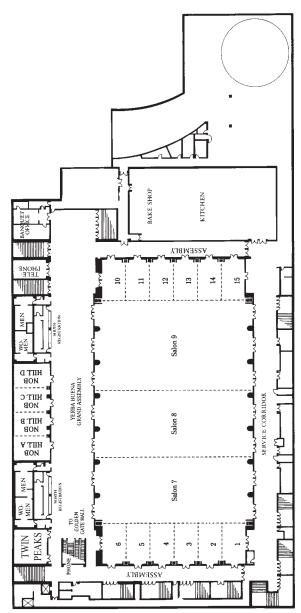

| Hot                              | tel Layout                                                                                        | 82      |  |

#### T1: Specifications and Figures of Merit for Mixed-Signal Circuits— A Guide to Understanding Where the Numbers Come from and What They Mean.

This tutorial explores specifications of mixed-signal circuits featured at ISSCC. An overview is provided of what the specification means, what makes the specification important for a given circuit, what is easy and what is difficult, and what to watch for when specs are quoted. Different "Figures of Merit" (where specifications are combined) are considered. Performance benchmarks from past (and present) ISSCCs are provided. Specifications of A/D converters, D/A converters, amplifiers, filters, VCOs and phase-locked loops are discussed.

**Instructor: David Robertson** is Product Line Director of the High Speed Converter Group at Analog Devices, Inc. He received BA and BE from Dartmouth College, in 1984 and 1985 respectively, and since 1985 has worked at Analog Devices as a design and product engineer on a wide variety of D/A and A/D converters on complementary bipolar, BiCMOS and CMOS processes. He holds 14 patents on converter and mixed-signal circuits, has participated in two Best Panel ISSCC Evening Panel Sessions, and is co-author of a paper that received the JSSC 1997 Best Paper Award.

#### T2: Design for Reliability in CMOS VLSI

As VLSI continues to scale, the likelihood of chip failure increases dramatically. At the same time, consumers expect electronic systems will be increasingly reliable. Rather than being confined to technical conferences and publications, reliability failures of high-profile computer systems now make headline news. This tutorial reviews the most common failure mechanisms and terms used to describe them. It describes three categories of reliability: (1) hard failures induced by alpha particles and cosmic ray neutron hits, and (3) circuit failures caused by mechanisms such as leakage sensitivity and thermal hot spots. For each of these failure mechanisms, strategies are considered for analysis and design-around.

**Instructor: David Greenhill** is Senior Engineer of Sun Microsystems UltraSparc design team in Sunnyvale, CA. In 1986, he graduated from Imperial College, London, with Physics BSc. From 1986 to 1992, he worked for INMOS in Bristol, England, on CMOS VLSI design, color lookup tables, video controllers, and transputer microprocessor design. He joined Sun Microsystems in 1992 and worked on the UltraSparcl and UltraSparcII designs. He is currently Chief Engineer for the implementation of UltraSparcV. His interests include high-performance CMOS circuit design and technology, CAD and reliability of high-performance multiprocessor computer systems. He is involved in circuit analysis and design tradeoffs for reliability in these systems. He has been a member of the ISSCC Program Committee since 1997.

#### T3: High-Dynamic-Range Image Sensors

This tutorial provides a framework for analyzing performance of image sensor dynamic range (DR) extension techniques and for comparing their effectiveness. A brief introduction to conventional image sensors, such as CCDs, CMOS APS and DPS is provided. A model is given for the signal path through an image sensor from input photocurrent to output voltage, including signal integration, dark current, temporal noise, and FPN. The model is used to define DR and SNR. Techniques for extending image sensor DR, including well-capacity adjusting, spatially-varying pixel exposure, time to saturation, and multiple capture are described. These techniques suffer from higher loss in SNR than others, which limits their effective DR extension. Comparisons based on other critera such as spatial resolution and implementation complexity are discussed. Other types of high-DR sensors, e.g., logarithmic sensors and silicon retina, are discussed. Recent research in the area is covered.

**Instructor:** Abbas El Gamal received BS EE from Cairo Univ. in 1972, MS in statistics and PhD in EE from Stanford in 1977 and 1978, respectively. From 78-80 he was Asst. Prof. of EE at Univ. of Southern California. He joined Stanford in 1981, where he is now Prof. of EE. From 1984-8, on leave from Stanford, he was Director of LSI Logic Research Lab, cofounder and Chief Scientist of Actel. From 1990-1995 he was a cofounder and Chief Technical Officer of Silicon Architects (now part of Synopsys). He is principal investigator on the Stanford Programmable Digital Camera Project. His research interests include: CMOS image sensors and digital camera design, image processing, network information theory, and electrically-configurable VLSI design and CAD. He has authored or coauthored over 100 papers and 25 patents in these areas. He serves on the board of directors and advisory boards of several IC and CAD companies. He is Fellow of the IEEE and member of the ISSCC Program Committee.

#### T4: Ferroelectric Memory Design (FeRAM 101)

FeRAMs are nonvolatile memories that compete favorably today with EEPROMs and Flash memories in terms of write speed and power consumption. This tutorial covers the basics of ferroelectric materials, ferroelectric capacitors as circuit elements, ferroelectric memory cell circuits and their read/write operations, reference generation, and FeRAM architectures.

**Instructor:** Ali Sheikholeslami is an Asst. Prof. of ECE at the Univ. of Toronto. His research interests are VLSI memory design (including SRAM, DRAM, and content-addressable memories), ferroelectric memory design (circuit design and modeling), multiple-valued memories, and high-speed signaling. He has several journal and conference papers and two US patents in the area of ferroelectric memories.

#### T5: Architectures and Design Methods for Cryptography

As electronic systems evolve from centralized to distributed, communicating devices, the need for security and encryption grows. This tutorial introduces the basics of cryptographic algorithms, the specialized mathematics involved, and the protocols commonly used today (e.g., SSL and IPsec). The tutorial then maps the various functions and protocols to VLSI architectures and describes different implementation techniques.

**Instructor: Ingrid Verbauwhede**, Univ. of California, Los Angeles, received PhD from K. U. Leuven, Belgium in 1991. From 1992-1994, she was visiting post-doc researcher at U.C. Berkeley. From 1994 to 1998, she was Principal Engineer at TCSI and ATMEL, and in 1998, joined UCLA as Assoc. Prof. Her current interest is architecture design, design methods and VLSI implementation of specialized processors for wireless communication, networking and encryption.

**Instructor: Jim Goodman**, Lumic Electronics, Ottawa, Canada, received PhD from MIT in 2000, where his research focused on reconfigurable energy-efficient VLSI architectures for cryptography. From 2000 to 2001 he was Senior IC Architect at Chrysalis-ITS, developing next-generation network security processors. He is currently Senior Mixed Signal Architect at Lumic Electronics, developing low-power multimedia processors.

#### T6: Introduction to Wireless-Receiver Design

An introduction to integrated receivers focuses on performance requirements for GSM cellular handset applications: (1) Overview of radio standards for sensitivity, blocking, AM suppression, and intermodulation. (2) Comparison of heterodyne, direct conversion, and low-IF receiver architectures. (3) Discussion of design specifications and tradeoffs.

**Instructor: G. Tyson Tuttle**, Silicon Labs, Austin TX holds an MS from UCLA and a BS from John Hopkins Univ., both in EE. He has held positions at Crystal Semiconductor and Broadcom Corp. focusing on high-speed mixed-signal circuit design for hard disk drive read channel and Ethernet applications. He joined Silicon Labs in 1997 where he is currently Product Manager for CMOS cellular wireless transceiver ICs. He holds 6 patents, is author or co-author of 6 technical publications, and is a member of IEEE.

#### **T7: CMOS Optical-Front-End Circuits**

This tutorial provides analysis of CMOS integration techniques and their limitations for optical-front-end circuits: (1) Discussion of transimpedance amplifiers and their optimization for speed and sensitivity. (2) Description of decision networks for data-recovery and its problems. (3) Examples and implementations of CMOS Gb/s circuits.

**Instructor: Michel Steyaert** received his PhD in Electronics from Katholieke Universiteit Leuven in 1987. In 1988 he was Visiting Asst. Prof. at the University of California, Los Angeles. From 1989-1996 he was NFWO Senior Research Associate at the ESAT Lab., K. U. Leuven, where he is now Professor. His research interests are high-frequency analog integrated circuits for high-frequency signal processing and for telecommunication circuits.

### SSCTC WORKSHOP ON ANALOG TELECOM

#### W1: Analog Telecom-Access Circuits and Concepts IEEE Solid State Circuits and Technology Committee Workshop

Organizing Chair: Jan Sevenhans, Alcatel Belgium, IEEE Fellow Committee: Paul Davis, Consultant; Trudy Stetzler, TI; Franz Dielacher, Infineon, Villach; Cormac Conroy, Berkana Wireless; Behzad Razavi, UCLA; Michiel Steyaert, KULeuven; Russ Apfel, Legerity; Anantha Chandrakasan, MIT; Stan Schuster, IBM, Bryan Ackland, Agere

The analog design community faces challenges of requirements for analog front-end building blocks such as high-voltage high-performance high-efficiency line drivers, high-resolution high-speed A/D and D/A converters, and upstream/downstream filters.

The major success of DSL technology worldwide places all telecom manufacturers under pressure for next-generation DSL products: increasing density of the lines per board, reducing power consumption per line and maximizing loop reach and robustness against disturbances such as RFI and bridge taps.

DMT signalling has opened golden gates on copper cable but leaves the system with a power bottleneck in the line drivers because of the high crest factor. Class A/B amplifiers, still in ADSL production lines, will soon be replaced with Class G, Class H, Class K and other high-efficiency power amplifier concepts re-invented today, going back to the future and remembering audio low-power high-efficiency concepts.

Loop-reach requirement push analog designers to achieve 14b-resolution A/D and D/A converters in high-volume-production highly-integrated analog front ends. Sigma-delta pipelined and various subranging architectures at the interface between analog and digital are revisited in advanced research programs. FDM upstream/downstream filtering is reconsidered to avoid carrier attenuation in the filter overlap region and the consequent loss of loop reach.

Speakers from telecom and silicon industry and from university research centers bring attendees up to date on the analog challenges of this emerging access application.

| W1 (Continued)                                                                                                                               |                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| <u>Topics</u><br>Welcome & Introduction                                                                                                      | <u>Time</u><br>8:30-8:45 |  |  |

| Trade Offs in ADSL Analog Front-End Requirements<br>Peter Reusens, Alcatel, Antwerp, Belgium                                                 | 8:45-9:30                |  |  |

| Analog Design Challenges in ADSL Filter and<br>Low-Noise Circuits.<br>Samuel Sheng, LSI Logic, San Jose, CA                                  | 9:30-10:15               |  |  |

| BREAK                                                                                                                                        | 15 min                   |  |  |

| ADSL Transceivers : Optimizing Power, Cost,<br>Function and Performance<br>Russell Apfel, Legerity, Austin, TX                               | 10:30-11:15              |  |  |

| ADSL Line Transceivers, Power and RX<br>Integration Trends<br>Marco Corsi, Texas Instruments, Dallas, TX                                     | 11:15-12:00              |  |  |

| LUNCH                                                                                                                                        | 12:00-2:00               |  |  |

| Silicon Technologies and Circuit Topologies<br>for High Efficiency in ADSL Line Drivers<br>Domenico Rossi, STMicroelectronics, Agrate, Italy | 2:00-2:45                |  |  |

| Line Drivers for xDSL<br>Tim Piessens, K.U. Leuven, Leuven, Belgium                                                                          | 2:45-3:30                |  |  |

| AFE Design for VDSL: a Case Study<br>Joerg Hauptman, Infineon, Villach, Austria                                                              | 3:30-4:15                |  |  |

| BREAK 15 min                                                                                                                                 | I                        |  |  |

| Concluding panel: DSL Analog Strategy of the<br>Future.                                                                                      | 4:30-5:30                |  |  |

| Conclusion                                                                                                                                   | 5:30                     |  |  |

#### SE1: Inductance: Implications and Solutions for High-Speed Digital Circuits

Co-Organizer/Co-Chair: William J Bowhill, Intel Corp., Shrewsbury, MA Co-Organizer: Anantha Chandrakasan, MIT, Cambridge, MA Co-Chair: Stephen Kosonocky, IBM, Yorktown Heights, NY

Technology scaling is realizing designs containing hundreds of millions of transistors capable of multi-GHz operation. For high-slew-rate signaling with low-resistance interconnects, on-chip inductance is no longer negligible. This session provides a comprehensive overview and describes practical approaches an IC designer can use to include inductance effects in chip designs.

The session begins with an overview of the extraction and analysis issues related to on-chip inductance effects, followed by a description of a partial-element equivalent circuit (PEEC) interconnect model and how these can be used for construction of a comprehensive model that includes portions of the power and ground grid surrounding the signal net and return path.

Techniques for managing the effects of inductance in the context of general on-chip busses are also described which provide the IC designer with the necessary methods, rules of thumb, and back-end tool checks to both constrain their effects in the front-end design phase and verify their correctness in the back-end prior to tape out.

A special section dedicated to clock network modeling describes clock distribution strategies which now require well-optimized and controlled onchip transmission line design. This includes a description of a full-wave PEEC interconnect analysis tool combined with 3D visualization for studying high-frequency effects.

Scaling trends in VLSI have created significant challenges for chip power delivery and distribution as supply voltages have decreased. Accurate modeling of the power distribution network becomes important, which includes information about the entire distribution network, decoupling capacitors hierarchies, board and package planes, vias, and bumps. The final session describes constructs to build power distribution models, the trade-offs and some design solutions to typical problems.

| <u>Topics</u><br>Inductance Extraction and Modeling<br>David Blaauw, Univ. of Michigan<br>Kaushik Gala, Motorola Inc., Austin, TX | <u>Time</u><br>7:30 PM |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|

| <b>On-chip Signaling</b><br>Shannon Morton, Silicon Graphics, Boston, MA                                                          | 8:00 PM                |

| <b>Clock Distribution</b><br>Phillip Restle, IBM, Yorktown Heights, NY<br>Xuejue Huang, Univ. California, Berkeley, CA            | 8:30 PM                |

| The Chip Electrical Interface<br>Claude Gauthier, Sun Microsystems, Sunnyvale, CA.<br>Brian Amick, Sun Microsystems, Austin, TX   | 9:00 PM                |

#### SE2: Low-Voltage Design for Portable Systems

Organizer/Co-Chair: Wanda Gass, Texas Instruments, Dallas, TX, USA Co-Chair: Thucydides Xanthopoulos, Cavium Networks, Marlboro, MA, USA

The processing requirements of portable devices are increasing at a fast pace as new algorithms, higher data rates and new system features are introduced. Technology scaling, in addition to low- power requirements for battery-powered devices, make low-voltage operation a design requirement.

In the past, there has been reliance on process and technology improvements to support increased circuit performance and lower power dissipation. Further technology-driven gains will come at an increased cost, necessitating better design practices.

Analog and RF designers are continuously challenged to design circuits using very low voltages, while still maintaining large dynamic ranges. New architectures and innovative uses of passive elements will be required to satisfy stringent product specifications.

On the digital side, the challenge is to continue improving performance as well as maintaining low leakage. Back biasing techniques in addition to device stacking, multiple threshold device usage and supply voltage gating can control standby and active leakage currents in deep submicron processes.

In addition, low-voltage operation reduces noise margins, and smaller feature sizes increase susceptibility to various noise sources. The resulting noise effects require accurate modeling and design considerations to ensure robust circuit operation.

The panelists enumerate and describe the challenges that lie ahead as application demand for performance, small feature sizes, and long battery life pose conflicting requirements to circuit and system designers. In addition, they address potential solutions to the aforementioned issues.

| <u>Topics</u><br>Technology, Architecture and Applications<br>Robert Brodersen, Prof., Univ. of California,<br>Berkeley, CA, USA | <u>Time</u><br>7:30 PM |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------|

| When MOSFET Switches Become MOSFET<br>Dimmers<br>Dennis Buss, Vice President, Texas Instruments,<br>Dallas, TX, USA              | 8:00 PM                |

| <b>RF Circuits at Low Voltage</b><br><b>Asad Abidi</b> , Professor, Univ. of California,<br>Los Angeles, CA, USA                 | 8:30 PM                |

| Leakage Reduction in Digital CMOS Circuits<br>Shekhar Borkar, Intel Fellow and Director, Intel Corp,<br>Hillsboro, OR, USA       | 9:00 PM                |

| Robustness of Digital Circuits @ Low Voltage<br>Harry Veendrick, Research Fellow, Philips, Eindhoven,<br>The Netherlands         | 9:30 PM                |

#### PLENARY SESSION – INVITED PAPERS

Chair:

Associate Chair:

Tim Tredwell, Eastman Kodak Research Labs, Rochester, NY ISSCC Executive-Committee Chair Willy Sansen, Katholieke Universiteit Leuven, Leuven, Belgium ISSCC Program-Committee Chair

#### FORMAL OPENING OF CONFERENCE

8:30 AM

#### 1.1 Technology in the Internet Age 8:40 AM Dennis Buss, Texas Instruments, Dallas, Texas, USA

Internet electronic products have requirements different from those of personal computers (PCs). The increasing importance of Internet electronics is driving changes in development of IC technology. One important characteristic of the Internet Age is computational disaggregation. Whereas, over the past 20 years, PCs have been characterized by ever-increasing computation capabilities, emerging Internet electronic products are characterized by sufficient computation to achieve the function in a small, often portable, form factor. The imperative for lower cost, which enables penetration into mass markets, is a second area where Internet electronic products differ from PCs. Disaggregation and cost requirements are driving an unprecedented degree of systemon-a-chip (SoC) integration. In the Internet Age, SoC integration means more than integrating different digital cores. It also means integrating functions that are realized today in different technologies: logic, memory, analog, power management, passives and radio or wireline driver, depending on the product. Because SoC integration is motivated primarily by cost, diverse functions must be integrated together in standard CMOS with minimal cost addition. Cost-effective embedded memory technology also needs to be developed. Current examples of SoC integration include cell phones, cable/DSL modems, and internet audio. These representative examples, together with others, are driving changes in the way ICs are developed. In the latter half of the decade, it is likely that SoC integration will expand to include MEMS, microphotonics, and on-chip energy sources. Moore's Law scaling will continue at least through the end of this decade, but SoC integration will become an increasingly important technology imperative for continued cost reduction throughout the Internet Age.

ISSCC, SSCS, JSSC, & IEEE AWARD PRESENTATIONS 9:30 AM

BREAK 10:00 AM

#### 1.2 Semiconductor Memories for IT

#### 10:15 AM

C. G. Hwang, Samsung Semiconductor Memory, Yongin City, Korea

Information technology (IT) emerged from the 1970s based on mainframe computers. Since then, PCs and the Internet world have drastically expanded the IT industry along with rapid growth of network and communication technology. For almost all platforms, semiconductor memories have been a key enabling technology.

In the PC era, DRAM density increase has been driven by rapid expansion of applications with advanced operating systems. In the future, servers will continue driving high-density DRAM requirements, and the maximum memory size of servers will be one of the key performance parameters. 512Mb DRAM will be widely available in 2002 and 16Gb DRAM is expected to appear within the next 10 years.

Performance of semiconductor memories will be driven by graphics applications and network systems. 1Gb/s/pin DRAM will be popular in 2002 and 2Gb/s/pin in 2004 for high-end graphics applications. Randomaccess times in the range of 5ns for SRAM and 20ns for DRAM range and 1Gb/s/pin DRAM will be available in 2002, and even faster (frequency, latency) memories will be required for high-end network systems such as OC-768-based switches and routers and beyond.

Mobile platforms, especially 3G phones and PDAs, are driving lowvoltage low-power memories. Standby power of DRAM and pseudo-SRAM has been reduced drastically over the last 2 years. 1.8V DRAM will be in volume production in 2002 and 1.0V DRAM is expected in 2005 for longer battery life and moving-picture capability of mobile applications. The small-form-factor requirement of mobile phones and consumer applications such as PDA, and DSC will expedite various multi-chippackage SRAM+Flash, solutions such as DRAM+Flash. and SRAM+DRAM+Flash. Recent digital convergence and the rapid reduction of \$/MB of mass storage flash memory increased the usage of flash memory in various mobile and consumer applications.

Semiconductor Memory will continue to follow Moore's law for at least the next 10 years and will be lead by mass storage flash memory technology. Memory requirement of various IT platforms will continue to increase the trend of MB/system and MB/person.

#### 1.3 Ambient Intelligence: the Next Paradigm for Consumer Electronics: How will it Affect Silicon? Fred Boekhorst, Philips Research, Eindhoven, The Netherlands 11:05 AM

Ambient Intelligence refers to an environment where the user experience is what matters. People want to have fun, feel free, enjoy life, feel secure, be in control and be productive. This experience is not linked to one particular device but is realized by a network of devices present in the environment that will provide us these experiences in an intelligent way.

Ambient Intelligence is introduced as a new paradigm in consumer electronics. Some of the technologies required for Ambient Intelligence are covered, with a focus on IC consequences. Ongoing work in three fields is described: ubiquitous radio, intuitive user/system interfaces and three-dimensional visual displays. These three fields highlight the diverse nature of Ambient Intelligence technologies as well as the resulting requirements for ICs. Considerations with respect to an introduction timeline of Ambient Intelligence are given.

#### BREAK 11:55 AM

#### IMAGE SENSORS

#### Chair: Charles V. Stancampiano, Eastman Kodak, Rochester, NY Associate Chair: Yoshiaki D. Hagiwara, Sony Corp., Tokyo, Japan

#### 2.1 A 1/1.8" 3M-pixel FT-CCD with On-Chip Horizontal Sub-Sampling for DSC Applications

1:30 PM

L. Le Cam<sup>1</sup>, J. Bosiers<sup>1</sup>, A. Kleimann<sup>1</sup>, H. van Kuijk<sup>1</sup>, J. Maas<sup>1</sup>, M. Beenhakkers<sup>1</sup>, H. Peek<sup>1</sup>, P. van de Rijt<sup>1</sup>, A. Theuwissen<sup>1,2</sup> <sup>1</sup>Philips Semiconductors, Eindhoven, The Netherlands <sup>2</sup>Delft Univ. of Technology, The Netherlands

A 1/1.8" 3M-pixel frame-transfer CCD (FT-CCD) has on-chip horizontal sub-sampling. It allows an additional preview mode where the image extraction rate is doubled (up to 60 images/s) while keeping the classic readout frequency of 25MHz. High-sensitivity video clips, fast auto-focus, and auto-exposure is achieved on digital still cameras.

#### 2.2 Single-Chip CMOS Image Sensor for Mobile Applications

2:00 PM

*K.* Yoon<sup>1</sup>, *C. Kim*<sup>1</sup>, *B. Lee*<sup>2</sup>, *D. Lee*<sup>1</sup> <sup>1</sup>Hynix Semiconductor Inc., Ichon Korea <sup>2</sup>National Semiconductor, Santa Clara, CA

A CIF CMOS Image sensor contains fundamental color signal processing functions on-chip. The analog line memory, which can be accessed twice, enables simple color-interpolation and other signal processing in a small chip. At 30frames/s, the sensor consumes 20mW at 3.0V supply.

#### 2.3 Single Chip for Imaging, Color Segmentation, Histogramming, and Pattern Matching

2:30 PM

*R. Etienne-Cummings*<sup>1,2</sup>, *P. Pouliquen*<sup>1,2</sup>, *M. Anthony Lewis*<sup>2</sup> <sup>1</sup>Johns Hopkins Univ., Baltimore, MD <sup>2</sup>Iguana Robotics, Inc., Baltimore, MD

128(H)x64(V) x RGB CMOS imager is integrated with region-of-interest selection, RGB-to-HSI transformation, HSI-based pixel segmentation, 36-bins x 12b HSI histogramming, and sum-of-absolute-difference template matching. 32 learned color templates are stored and compared to each frame. At 30frames/s, it uses 1mW.

BREAK 3:00 PM

#### 2.4 138dB-Dynamic-Range CMOS Image Sensor with New Pixel Architecture

3:15 PM

D. Stoppa, A. Simoni, L. Gonzo, M. Gottardi, G. Dalla Betta Loc. Pante' di Povo, Trento, Italy

A 128x64 pixel image sensor in  $0.35\mu m 3.3V$  CMOS technology achieves 138dB dynamic range by adapting single-pixel integration time to the local illumination conditions. Video frame rate is achieved with 0.2% rms temporal noise and 14mW power in a test chip.

#### 2.5 1.5M Pixel Imager with Localized Hole-Modulation Method 3:45 PM

T. Miida, K. Kawajiri, H. Terakago, T. Endo, S. Yamamoto, T. Okazaki, A. Nishimura Innotech Corp., Yokohama, Japan

A 1.5Mpixel imager with 4.2µm square pixel is composed of a single MOSFET and a pinned photo-diode. A localized high-density p-region near the source of MOSFET converts the accumulated hole number to source voltage. Low random noise, low dark signal, high sensitivity with good color reproduction and resolution are achieved.

#### 2.6 A 1.0V V<sub>DD</sub> CMOS Active-Pixel Image Sensor with Complementary-Pixel Architecture Fabricated with a 0.25μm CMOS Process 4:00 PM

C. Xu, M. Chan

Hong Kong Univ. of Science & Technology, Clear Water Bay, Hong Kong

A 128x128 complementary CMOS active-pixel sensor (CAPS) is fabricated in 0.25 $\mu$ m CMOS for low -voltage application. A single-slope with correlated double sampling (CDS) is used in the readout circuit. The chip operates at a V<sub>DD</sub> as low as 0.8V with 15dB added dynamic range compared with conventional CMOS APS.

#### 2.7 A CCD Image Sensor of 1Mframes/s for Continuous Image Capturing of >100 Frames 4:15 PM

T. Goji Etoh<sup>1,2</sup>, D. Poggemenn<sup>2</sup>, A. Ruckelshausen<sup>2</sup>, A. Theuwissen<sup>3,6</sup>,

G. Kreider<sup>3</sup>, H.-O. Folkerts<sup>3</sup>, H. Mutoh<sup>4</sup>, Y. Kondo<sup>5</sup>, H. Maruno<sup>5</sup>,

K. Takubo<sup>5</sup>, H. Soya<sup>5</sup>, K. Takehara<sup>1</sup>, T. Okinaka<sup>1</sup>, Y. Takano<sup>1</sup>,

T. Reisinger<sup>1,2</sup>, C. Lohmann<sup>1,2</sup>

<sup>1</sup>Kinki Univ., Higashi-Osaka, Japan

<sup>2</sup>Univ. of Applied Sciences, Osnabrueck, Germany

<sup>3</sup>Philips Semiconductors, The Netherlands

<sup>4</sup>Link Research Corp., Japan

<sup>5</sup>Shimadzu Corp., Japan

<sup>6</sup>Delft Univ. of Technology, The Netherlands

A single-chip CCD image sensor captures >100 successive images at >1Mframes/s. The pixel count of the test chip is 312 x 260 (=81,120) pixels. Charge handling capacity is 40k electrons. Grey levels are 10b. Fill factor is 13%. On-chip overwriting mechanism makes possible continuous recording of the latest image signals, draining the old ones to the substrate.

#### 2.8 A 35mm-Film Format CMOS Image Sensor for Camera-Back Applications 4:30 PM

J. Hurwitz, M. Panaghiston, K. Findlater, R. Henderson, T. Bailey STMicroelectronics, Edinburgh, Scotland, UK

A 5V 1120x1808 pixel 35mm-film format CMOS image sensor for cameraback use, fabricated in 0.5 $\mu$ m 2P3M technology, includes integrated light detection circuitry using non-destructive pixel read and consumes <50 $\mu$ W. Reticle stitching is employed for the large format. Dynamic range is 66dB and peak SNR is 55dB.

#### CONCLUSION 4:45 PM

#### DIGITAL SIGNAL PROCESSORS, CIRCUITS, AND SYSTEMS

#### Chair: Willie Anderson, Analog Devices, Austin, TX Associate Chair: Steve Morein, ATI Research, Marlborough, MA

#### 3.1 A Packet-Memory-Integrated 44Gb/s Switching Processor with 10Gb Port and 12 1Gb Ports

1:30 PM

M. Lau, S. Shieh, P. Wang, B. Smith, M. Yuan, D. Lee, J. Gaba, J. Chao, B. Shung, C. Shih

Broadcom Corp., San Jose, CA

A 44Gb/s switching processor chip has 1MB embedded packet memory. With a 10Gb and 12 1Gb ports, this chip is useful for LAN/WAN bridging applications. Wirespeed switching performance is demonstrated using a shared buffer switching architecture. This 0.18µm CMOS processor integrates a 10Gb port with an XGMII interface.

#### 3.2 A 6GOPS General-Purpose DSP with an Enhanced Instruction Set for Wireless Communication

2:00 PM

F. Lange, A. Olofsson, M. Jalfon, H. Meirov, A. Kadry, D. Agur, O. Chalak, T. Ben-Nun Glass, R. Holzer, O. Raikhman, D. Agur, Z. Greenfield Analog Devices, Herzelia, Israel

A 6GOPS DSP implements the TigerSharc architecture with an instruction set enhanced for wireless communication. It is implemented in a  $0.13 \mu m$  process with 8 layers of copper interconnect and operates at 250MHz with 1W power dissipation under nominal conditions.

#### 3.3 A 600MHz VLIW DSP

#### 2:30 PM

S. Agarwala, P. Koeppen, T. Anderson, A. Hill, M. Ales, L. Simar, R. Damodaran, L. Nardini, P. Wiley, S. Mullinnix, J. Leach, A. Lell, M. Gill, J. Golston, D. Hoyle, A. Rajagopal, A. Chachad, M. Agarwala, R. Castille, N. Common, J. Apostol, H. Mahmood, M. Krishnan, D. Bui Texas Instruments, Dallas, TX

A 600MHz VLIW DSP delivers 4800MIPS, 2400 (16b) or 4800 (8b) million multiply accumulates at 0.3mW/MMAC (16b). The chip has 64M transistors and dissipates 718mW at 600MHz and 1.2V, and 200mW at 300MHz and 0.9V. It has an 8-way VLIW DSP core, a 2-level memory system, and an I/O bandwidth of 2.4GB/s.

#### BREAK 3:00 PM

#### 3.4 A 175mV Multiply-Accumulate Unit Using an Adaptive Supply Voltage and Body Bias (ASB) Architecture

3:15 PM

*M. Miyazaki<sup>1,2</sup>, J. Kao<sup>1</sup>, A. Chandrakasan<sup>1</sup>* <sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA <sup>2</sup>Hitachi Ltd., Tokyo, Japan

The power dissipation of a digital circuit is minimized by simultaneous control of power supply voltage and body bias. The technique minimizes power dissipation for varying processing rates through dynamic adjustment of V<sub>dd</sub> and V<sub>bb</sub>. A 16b MAC operates at 166kHz and 14nW at 175mV V<sub>dd</sub>. A ring oscillator operates at 0.1V.

#### 3.5 A 1.3GSample/s Full-Rate Self-Timed 10-Tap FIR with Variable Latency and Clocked Interfaces 3:45 PM

*J. Tierno<sup>1</sup>, A. Rylyakov<sup>1</sup>, S. Rylov<sup>1</sup>, M. Singh<sup>2</sup>, P. Ampadu<sup>3</sup>, S. Nowick<sup>2</sup>, M. Immediato<sup>1</sup>, S. Gowda<sup>1</sup> <sup>1</sup>IBM, Yorktown Heights, NY <sup>2</sup>Columbia Univ., New York, NY <sup>3</sup>Cornell Univ., Ithaca, NY*

A 6b 10-tap digital FIR has a self-timed datapath, clocked interfaces, and variable latency. The  $0.45 \text{mm}^2$  circuit in  $0.18 \mu \text{m}$  CMOS is operational form 1.2V to 2.1V power supply, and has 80mW dissipation at 300MSample/s and 4 cycles of latency, and 500mW at 1.3GSample/s and 7 cycles of latency.

#### 3.6 A GSM/GPRS Mixed-Signal Baseband IC

4:15 PM

D. Redmond, M. Fitzgibbon, A. Bannon, D. Hobbs, C. Zhao, K. Kase, J. Chan, M. Priel, K. Traylor, K. Tilley Motorola, Austin, TX

A dual-core baseband processor IC for GSM/GPRS cellular phone applications is built in a 0.13µm CMOS process with 5 levels of copper interconnect and contains a high level of mixed signal integration which includes: 1GHz CMOS synthesizer, 10b general-purpose ADC, two 14b ADCs, power amplifier controller, and 13b voice CODEC.

#### 3.7 A 0.55nV/Hz Gigabit Fully-Differential CMOS Preamplifier for MR/GMR Read Application

4:45 PM

Z. Zheng, S. Lam, S. Sutardja Marvell Semiconductor, Inc., Sunnyvale, CA

A low-noise Gb fully-differential preamp in 0.25µm CMOS has a variable gain with constant 850MHz bandwidth, and has a variable bandwidth with constant gain. Noise is <0.55nV/Hz. The power consumption is 600mW. The die of a 4-channel IC is <4.2mm<sup>2</sup>.

CONCLUSION 5:15 PM

### BACKPLANE INTERCONNECTS AND CLOCK MULTIPLIERS

#### Chair: Wai Lee, Texas Instruments, Dallas, TX Associate Chair: Mehmet Soyuer, IBM, Yorktown Heights, NY

#### 4.1 A 1.5V 86mW/ch 8-Channel 622-2500Mb/s/ch CMOS SerDes Macrocell with Selectable MUX/DEMUX Ratio 1:30 PM

F. Yang, J. O'Neill, P. Larsson, D. Inglis, J. Othmer Agere Systems, Holmdel, NJ

An 8-channel serial link transceiver realizes 20Gb/s full duplex total I/O throughput with <700mW dissipation from a 1.5V supply and occupies 2mm<sup>2</sup> in 0.16µm CMOS. An analog DLL allows tracking of frequency offset up to 400ppm. The receiver, employing an integrate-and-dump front-end. achieves a 30mVpp sensitivity.

#### 4.2 Quad 3.125Gb/s/channel Transceiver with Analog Phase Rotators 2:00 PM

D. Zheng, X. Jin, E. Cheung, M. Rana, G. Song, Y. Jiang, Y. Sutu, B. Wu BitBlitz Communications, Fremont, CA

A 0.18µm<sup>2</sup> CMOS quad transceiver provides 12.5Gb/s full-duplex raw data throughput at 200mW/channel consumption. An analog phase rotator in CDR eliminates quantization error of digital phase interpolation techniques, resulting in <17ps peak-peak output jitter.

#### 4.3 A 62Gb/s Backplane-Interconnect ASIC Based on 3.1Gb/s Serial-Link Technology 2:30 PM

*P. Landman*<sup>1</sup>, *A. Yee*<sup>1</sup>, *R. Gu*<sup>1</sup>, *B. Parthasarathy*<sup>1</sup>, *V. Gupta*<sup>1</sup>, *S. Ramaswamy*<sup>1</sup>, *L. Dyson*<sup>1</sup>, *P. Bosshart*<sup>1</sup>, *J. Reynolds*<sup>1</sup>, *M. Frännhagen*<sup>2</sup>, *P. Fremrot*<sup>2</sup>, *S. Johansson*<sup>2</sup>, *K. Lewis*<sup>2</sup>, *W. Lee*<sup>1</sup>

<sup>1</sup>Texas Instruments, Dallas, TX

<sup>2</sup>Turin Networks, Petaluma, CA

A backplane interconnect ASIC with 62Gb/s full-duplex aggregate throughput uses 3.1Gb/s serial link technology organized as 20 bidirectional channels to realize bandwidth. The chip operates with <5×10<sup>-17</sup> aggregate BER and is fabricated in a 0.18µm CMOS technology, dissipating 9W in a 768-pin flipchip BGA package.

#### BREAK 3:00 PM

#### An 800Mb/s Physical-Layer LSI with Hybrid Port Architecture 4.4 for Consumer Electronics Networking

3:15 PM

T. Yoshikawa, T. Yoshida, T. Ebuchi, Y. Arima, T. Iwata, K. Nishimura, H. Kimura, Y. Komatsu, H. Yamauchi Matsushita Electric, Osaka, Japan

A physical layer LSI has one DS-port and two ßports in accordance with IEEE1394-2000 and P1394b Draft 1.01 respectively. The 0.25µm CMOS LSI realizes 800Mb/s and 1.2km peer-to-peer IEEE1394 networking through ßport. Each ßport requires 180mW active power and is trea ted as ASIC macro for future large system integration.

#### 4.5 A 0.2-2GHz 12mW Multiplying DLL for Low-Jitter Clock Synthesis in Highly-Integrated Data-Communication Chips 3:45 PM

R. Farjad-rad, W. Dally, J. Poulton, H. Ng, T. Stone, R. Nathan Velio Communications, Milpitas, CA

The MDLL, in 0.18µm CMOS, has 0.05mm  $^2$  active area and 200MHz to 2GHz speed range. The complete synthesizer, including the output clock buffers, dissipates 12mW from a 1.8V supply at 2.0GHz. This MDLL architecture is used as a clock multiplier in a highly-integrated chip, and has jitter of 1.73ps (rms) and 15.6ps (pk-pk) at 2GHz.

#### 4.6 A Multiple-Crystal-Interface PLL with VCO Realignment to Reduce Phase Noise

4:15 PM

S. Ye<sup>1</sup>, *L. Jansson<sup>2</sup>*, *I. Galton*<sup>1</sup> <sup>1</sup>Univ. of California, San Diego, CA <sup>2</sup>Silicon Wave, San Diego, CA

A phase realignment technique is applied to a ring oscillator VCO in a 3V 6.8mW CMOS PLL that converts most of the popular crystal reference frequencies to a 32MHz baseband clock and RF PLL reference. The peak in-band phase noise at 20kHz offset is -102dBc/Hz with the technique enabled, and -92dBc/Hz with the technique disabled.

#### 4.7 A Multichip-on-Oxide 1.0Gb/s Fully-Differential CMOS Transimpedance Amplifier for Optical Interconnect Applications

4:45 PM

J. Lee<sup>1</sup>, S. Song<sup>1</sup>, S. Min Park<sup>1</sup>, C. Nam<sup>2</sup>, Y. Kwon<sup>1</sup>, H. Yoo<sup>1</sup> <sup>1</sup>Korea Advanced Institute of Science and Technology (KAIST), Taejon, Korea

<sup>2</sup>Telephus, Taejon, Korea

A 1.0Gb/s 80dB $\Omega$  fully-differential TIA uses 0.25µm CMOS and multichipon-oxide (MCO) process. MCO enables integration of PD, TIA, and planar inductors of Q=21.1 for shunt peaking on an oxidized silicon substrate. Interchannel crosstalk and power dissipation are <-40dB and 27mW, respectively. MCO and TIA chips are 5x5mm<sup>2</sup> and 0.7x1mm<sup>2</sup>, respectively.

#### 4.8 45GHz SiGe Active Frequency Multiplier

5:00 PM

S. Hackl<sup>1,2</sup>, J. Boeck<sup>1</sup>, G. Ritzberger<sup>1,2</sup>, M. Wurzer<sup>1</sup>, H. Knapp<sup>1</sup>,

L. Treitinger<sup>1</sup>, A. L. Scholtz<sup>2</sup>

<sup>1</sup>Infineon Technologies AG, Munich, Germany

<sup>2</sup>Technical Univ. of Vienna, Vienna, Austria

A frequency quadrupler for frequencies up to 45GHz uses a preproduction  $0.4\mu m$  SiGe bipolar technology. Gain is achieved at -15dBminput power between 24 and 45GHz with maximum of 7.3dB at 44GHz. The circuit draws 84mA from a single 5V supply.

CONCLUSION 5:15 PM

#### WIRELESS NETWORKING TRANSCEIVERS

#### Chair: Mary Jo Nettles, Mobilian, San Diego, CA Associate Chair: Tom Schiltz, Linear Technology Corp., Colorado Springs, CO

#### 5.1 A Bluetooth Radio in 0.18µm CMOS.

1:30 PM

*P.* van Zeijl<sup>1</sup>, J. Eikenbroek<sup>1</sup>, P. Vervoort<sup>1</sup>, S. Setty<sup>2</sup>, J. Tangenberg<sup>1</sup>, *G. Shipton<sup>2</sup>*, *E. Kooistra<sup>1</sup>*, *I. Keekstra<sup>1</sup>*, *D. Belot<sup>3</sup>* <sup>1</sup>Ericsson Eurolab, Emmen, The Netherlands <sup>2</sup>Ericsson Microelectronics, Swindon, United Kingdom <sup>3</sup>STMicroelectronics, Crolles, France

A Bluetooth radio in 0.18µm CMOS technol ogy works on 2.5-3.0V, dissipating 75mW in RX and 90mW in TX. RX uses a 2MHz IF with an active poly-phase bandpass filter. The fractional-N PLL uses a VCO running at 5GHz. TX uses IQ modulation. Special attention is paid to Sicrosstalk because this radio is combined with baseband circuitry. Silicon area is 5.5mm<sup>2</sup>.

### 5.2 A Direct-Conversion Single-Chip Radio-Modem for Bluetooth

**2:00 PM** G. Chang<sup>1</sup>, L. Jansson<sup>1</sup>, K. Wang<sup>1</sup>, J. Grilo<sup>1</sup>, R. Montemayor<sup>1</sup>, C. Hull<sup>2</sup>, M. Lane<sup>1</sup>, A. X. Estrada<sup>1</sup>, M. Anderson<sup>1</sup>, I. Galton<sup>1</sup>, S.V. Kishore<sup>1</sup> <sup>1</sup>Silicon Wave Corp., San Diego, CA <sup>2</sup>now at National Semiconductor, San Diego, CA

A fully-integrated radio-modem using a direct-conversion receiver architecture achieves -83dBm sensitivity at 0.1% BER, +40dBm IIP2, and -5dB and -40dB adjacent and alternate channel blocking C/I, respectively. The radio consumes 39mA in receive and 37mA in transmit mode with a 2.7V supply. The 19.5mm<sup>2</sup> chip uses a 0.35µm 27GHz f  $_{\rm T}$  SOI BiCMOS process.

#### 5.3 Design of a Low-Cost Integrated 0.25µm CMOS Bluetooth SOC in 16.5mm<sup>2</sup> Silicon Area

2:30 PM

J. Cheah, E. Kwek, E. Low, C. Quek, M. Choke, C. Yong, R. Enright, J. Hirbawi, A. Lee, H. Xie, L. Wei, L. Luong, J. Pan, S-T. Yang, W. Ngai, A. Lau, L. Chew Transilica, San Diego, CA

A complete 0.25µm CMOS SOC bluetooth solution adopts a two -die in a single MCM chip packaging approach with minimum product cost as the most important design goal while maintaining competitive power consumption and RF performance.

BREAK 3:00 PM

#### 5.4 A 5GHz CMOS Transceiver for IEEE 802.11a Wireless LAN 3:15 PM

D. Su<sup>1</sup>, M. Zargari<sup>1</sup>, P. Yue<sup>1</sup>, S. Rabii<sup>1</sup>, D. Weber<sup>1</sup>, B. Kaczynski<sup>1</sup>, S. Mehta<sup>1</sup>, K. Singh<sup>1</sup>, S. Mendis<sup>1</sup>, B. Wooley<sup>2</sup> <sup>1</sup>Atheros Communications, Sunnyvale, CA <sup>2</sup>Stanford Univ., Stanford, CA

A 5GHz transceiver comprising the RF and analog circuits of an IEEE 802.11a-complaint WLAN using a 0.25µm CMOS technology occupies 22mm<sup>2</sup>. The IC has 22dBm maximum transmitted power, 8dB overall receive-chain noise figure, and -112dBc/Hz synthesizer phase noise at 1MHz offset.

#### 5.5 A 2.4GHz RF Transceiver with Digital Channel-Selection Filter for Bluetooth

3:45 PM

M. Kokubo, M. Shida, T. Ishikawa, H. Sonoda, K. Yamamoto, T. Matsuura, M. Matsuoka, T. Endo, T. Kobayashi, K. Oosaki, T. Henmi, J. Kudoh, H. Miyagawa Central Research Lab., Hitachi Ltd, Tokyo, Japan

An RF transceiver chip for Bluetooth that uses a digital channel-selection filter is 3.3x3.4mm<sup>2</sup>, realized by decrease of the analog area using the digital channel selection filter. The test chip uses 0.35µm BiCMOS.

## 5.6 Single-Chip 5.8GHz Electronic-Toll-Collection Transceiver IC with PLL and Demodulation Circuits

4:15 PM

T. Masuda<sup>1</sup>, K. Ohhata<sup>2</sup>, N. Shiramizu<sup>2</sup>, T. Maruyama<sup>3</sup>, S. Hanazawa<sup>3</sup>, M. Kudoh<sup>3</sup>, Y. Tanba<sup>3</sup>, Y. Takeuchi<sup>3</sup>, H. Shimamoto<sup>2</sup>, T. Nagashima<sup>4</sup>, K. Washio<sup>2</sup>

Hitachi, Ltd., <sup>1</sup>Kokubunji, Tokyo/ <sup>3</sup>Ome, Tokyo/ <sup>4</sup>Yokohama, Kanagawa, Japan

<sup>2</sup>Hitachi Device Engineering, Co. Ltd., Tokyo Japan

A single-chip 5.8GHz ETC transceiver IC with PLL and demodulator uses SiGe HBT/CMOS. The fully-integrated ETC chip includes a 31dB-gain RX stage, an ASK demodulator, and a high-precision RSSI. The PLL is constructed with a varactor-tuned LC-VCO and a low-power BiCMOS synthesizer. The TX stage incorporates a transformer-transferred singleended PA.

CONCLUSION 4:45 PM

#### NON-VOLATILE MEMORIES AND SRAM

#### Chair: Jagdish Pathak, Sub-Micron Circuits, San Jose, CA Associate Chair: Ban-Pak Wong, Sun Microsystems, Palo Alto, CA

#### 6.1 A 512Mb, NROM Data Storage Memory with 8MB/s Data Rate 1:30 PM

*E. Maayan<sup>1</sup>, R. Dvir<sup>1</sup>, J. Shor<sup>1</sup>, D. Avni<sup>1</sup>, B. Eitan<sup>1</sup>, E. Stein<sup>2</sup>, Z. Cohen<sup>3</sup>, M. Meyassed<sup>3</sup>, H. Palm<sup>3</sup>, Y. Alpern<sup>3</sup>.* <sup>1</sup>Saifun Semiconductors, Netanya, Israel <sup>2</sup>Infineon Technologies, Düsseldorf, Germany <sup>3</sup>Ingentix Semiconductor, Netanya, Israel

The NROM technology is applied to EEPROM, Flash, and data storage product lines. All the products are based on the two-bit-per-cell core technology, using common design concepts, algorithms, circuits, and the same process architecture. Differing product requirements emphasize versatility of the concept.

#### 6.2 A 44mm<sup>2</sup> 4-Bank 8-Word Page-Read 64Mb Flash Memory with Flexible Block Redundancy and Fast Accurate Word-Line Voltage Controller

**2:00 PM** *T. Tanzawa*<sup>1</sup>, *A. Umezawa*<sup>1</sup>, *T. Taura*<sup>1</sup>, *H. Shiga*<sup>1</sup>, *T. Hara*<sup>1</sup>, *Y. Takano*<sup>1</sup>, *T. Miyaba*<sup>2</sup>, *N. Tokiwa*<sup>2</sup>, *K. Watanabe*<sup>1</sup>, *H. Watanabe*<sup>1</sup>, *K. Masuda*<sup>1</sup>, *K. Naruke*<sup>1</sup>, *H. Kato*<sup>1</sup>, *S. Atsumi*<sup>1</sup> <sup>1</sup>Toshiba Corp., Yokohama, Japan <sup>2</sup>Toshiba Mircoelectronics Corp., Kawasaki, Japan

Combining a negative-gate channel-erasing NOR flash memory technology with an aggressively-scaled NAND flash process technology results in a 64Mb NOR flash memory with  $0.27\mu m^2$  cell and  $44mm^2$  chip. The flash memory provides 4 independent banks for flexible dual operation and unique block redundancy for yield.

#### 6.3 A 1.8V 1Gb NAND Flash Memory with 0.12µm Process Technology

2:30 PM

J. Lee, H. Im, D. Byeon, K. Lee, D. Chae, K. Lee, Y. Lim, J. Lee, J. Choi, Y. Seo, J. Lee, K. Suh Samsung Electronics, Yongin, Korea

A 1.8V 1Gb flash memory uses a  $0.12\mu$ m STI process technology. A charge pump operates at <1.8V. A center-placed row decoder is digitized in one block pitch by applying 32-cell NAND structure. A page buffer, containing two latches, supports cache-program to improve program speed to 7MB/s.

BREAK 3:00 PM

#### 6.4 A 125mm<sup>2</sup> 1Gb NAND Flash Memory with 10MB/s Program Throughput 3:15 PM

H. Nakamura<sup>1</sup>, K. Imamiya<sup>1</sup>, T. Himeno<sup>1</sup>, T. Yamamura<sup>1</sup>, T. Ikehashi<sup>1</sup>, K. Takeuchi<sup>1</sup>, K. Kanda<sup>1</sup>, K. Hosono<sup>1</sup>, T. Futatsuyama<sup>1</sup>, K. Kawai<sup>1</sup>, R. Shirota<sup>1</sup>, K. Shimizu<sup>1</sup>, N. Arai<sup>1</sup>, F. Arai<sup>1</sup>, K. Hatakeyama<sup>1</sup>, H. Hazama<sup>1</sup>, M. Saito<sup>1</sup>, H. Meguro<sup>1</sup>, K. Conley<sup>2</sup>, K. Quader<sup>2</sup>, J. Chen<sup>2</sup> <sup>1</sup>Toshiba, Yokohama, Japan <sup>2</sup>Sandisk, Sunnyvale, CA

A 125mm<sup>2</sup> 1Gb NAND flash uses  $0.13\mu$ m CMOS. The cell is  $0.077\mu$ m<sup>2</sup>. Chip architecture is changed to reduce chip size and to realize 10.6MB/s throughput for program and 20MB/s for read. An on-chip page copy function provides 9.4MB/s throughput for garbage collection.

#### 6.5 A Low-Power ROM using Charge Recycling and Charge Sharing 3:45 PM

*B-D. Yang, L-S. Kim* KAIST, Taejon, Korea

A charge-recycling predecoder (CRPD), a charge-recycling word line decoder (CRWD), and a charge-sharing bit line (CSBL) reduce power in a memory. The CRPD and the CRWD recycle the charge used in predecoder lines and word lines. The CSBL reduces the bit line swing voltage. A 128kb ROM in a 0.35µm CMOS process consumes 8.63mW at 100MHz and 3.3V.

#### 6.6 The 16kB Single-Cycle-Read-Access Cache on a Next-Generation 64b Itanium Microprocessor

4:15 PM

*D. E Bradley*<sup>1</sup>, *P. Mahoney*<sup>2</sup>, *B. Stackhouse*<sup>1</sup> <sup>1</sup>Hewlett Packard, Fort Collins, CO <sup>2</sup>Intel Corp., Fort Collins, CO

A 16kB four-ported physically addressed cache operates at 1.2GHz with 19.2GB/s peak bandwidth. Circuit and microarchitectural techniques are optimized to allow a single-cycle read access latency. The cache occupies 3.2x1.8mm<sup>2</sup> in a 0.18µm process.

#### 6.7 An On-Chip 3MB Subarray-Based 3<sup>rd</sup>-Level Cache for a Next-Generation 64b Itanium Microprocessor

4:45 PM

*D. Weiss*<sup>1</sup>, *J. Wuu*<sup>1</sup>, *V. Chin*<sup>2</sup> <sup>1</sup>Hewlett-Packard, Fort Collins, CO <sup>2</sup>Intel Corp., Santa Clara, CA

This 3MB on-chip level-three cache employs subarray design style, and achieves 85% array efficiency. Characterized to operate up to 1.2GHz, the cache allows a store and a load in every four core cycles, and provides a total bandwidth of 64GB/s at 1.0GHz.

CONCLUSION 5:15 PM

#### E1 Software Radio: Cool or to be Cooled? (Salon 1-6)

Organizer/ Moderator: Michel S.Steyaert, Katholieke Universiteit Leuven, Belgium

All system designers dream of flexibility and easy, fast system adjustment. They dream of performing wireless transceiver functions in software. This would mean no nasty analog circuits. However, more analog functions are appearing. Is it possible to put A/D and/or D/A converter immediately before or after the antenna? Will this result in an unacceptable power drain, or will the solution enable more-efficient transmission techniques?

Panelists:

Qiuting Huang, ETH Zurich, Lab, Switzerland Raf Roovers, Philips Research, Eindhoven, The Netherlands Franz Dielacher, Infineon Technologies, Villach, Austria Bram Nauta, Univ. of Twente, Enschede, The Netherlands Simon Atkinson, Analog Devices Inc., Wilmington, MA Hiroshi Tsurumi, Toshiba Corp., Corp. R&D Ctr., Kawasaki, Japan

#### E2 When Will Optical Interconnects Appear on High-Performance Microprocessors? (Salon 7)

Organizer: Stefanos Sidiropoulos, Aeluros Inc, Palo Alto, CA Moderator: Ian Young, Intel Corp., Hillsboro, OR

Performance of modern processors is limited not by intrinsic transistor speed, but by bandwidth and latency of internal and external interconnects. Optical interconnect technology promises virtually unlimited bandwidth. Will large-scale digital chips be forced to use optical interconnects on-chip and to the rest of the system? Will on-chip copper interconnects with mixed-signal I/O and DSP techniques enable microprocessors to remain purely electrical chips? Are the cost/performance advantages of opto-electronics attractive enough to overcome the inertia of a mature industry?

Panelists:

Alina Deutsch, IBM T. J. Watson Research Center, Yorktown Heights, NY Karl Joachim Ebeling, Infineon Technologies AG, Munich, Germany Mark Horowitz, Stanford Univ., Stanford, CA David A. Miller, Stanford Univ., Stanford CA Sam Naffziger, Hewlet Packard, Fort Collins, CO Mitsumasa Koyanagi, Tohoku Univ., Japan Christer Svensson, Linkoping Univ., Sweden

#### E3 Does Moore's Law Apply to Analog?: Past, Present, and Future Implications of Technology Progress and Higher Levels of Integration for Mixed-Signal Circuits

(Salon 8)

Co-organizer: Venu Gopinathan, Broadcom Corp., Irvine, CA Co-organizer, Moderator: David Robertson, Analog Devices, Wilmington, MA

Digital ICs have been governed by an increase in integration density obeying Moore's Law. Does the same law benefit the analog domain? Mixed-signal circuits care about SNR and dynamic range. Power dissipation is more than cv<sup>2</sup>f. Are constantly-shrinking lithographies a boon or a curse? What are the important issues for integration of mixed-signal circuits? What are the hard and soft limits? Will designs hit a wall in deep sub-micron where mixed-signal integration no longer makes sense?

Panelists:

Kerry Bernstein, IBM, Essex Junction, VT Lew Counts, Analog Devices, Wilmington, MA Steven J. Hillenius, Agere Systems, Murray Hill, NJ. Masao Hotta, Hitachi Ltd., Tokyo, Japan Ted Tewksbury, Maxim Integrated Products, N. Chelmsford, MA. Maarten Vertregt, Philips Research Labs, Eindhoven, The Netherlands Bruce Wooley, Stanford Univ., Stanford, CA

#### E4 Have Universities Killed Research - or Has Industry Corrupted It?

(Salon 9)

Organizer: Bud Taddiken, Microtune, Plano, TX Moderator: Thomas H. Lee, Stanford Univ., Stanford, CA

Discussion covers ways to improve university/industry interactions for research. Is industry getting what it needs from university research? Is academia getting what it needs or wants? Industry says that it wants long-range fundamental research, but seems more interested in paying for short-range applied research. Is it just money for students? Are there pure motives to build on?

Panelists:

Hugo J. De Man, KU Leuven/IMEC, Leuven, Belgium Herbert Eichfeld, Infineon Technologies AG, Munich, Germany Teresa H. Meng, Stanford Univ., Stanford CA J. Chris Ruddell, Consultant, Fremont, CA Eric Swanson, Consultant, Buda, TX

#### **BASEBAND COMMUNICATIONS**

Chair: Lars Thon, Atheros Communications, Sunnyvale, CA Associate Chair: Ivo Bolsens, Xilinx Inc., San Jose, CA

#### 7.1 A Unified Turbo / Viterbi Channel Decoder for 3GPP Mobile Wireless in 0.18µm CMOS

8:30 AM

*M. Bickerstaff, D. Garrett, T. Prokop, C. Thomas, B. Widdup, G. Zhou, C. Nicol, R. Yan* Lucent Technologies, North Rvde, Australia

A 3GPP-compliant 4.1Mb/s channel decoder supports data and voice calls in a unified Turbo/Viterbi architecture with hardware interleaver memory and pattern computation. The  $9mm^2$  chip in 0.18µm 1.8V 6LM CMOS operates at 110MHz and consumes 306mW when decoding 2Mb/s data and voice calls.

#### 7.2 An Integrated 802.11a Baseband and MAC Processor

9:00 AM

B. Baas, E. Cooper, J. Gilbert, G. Hsieh, P. Husted, A. Lokanathan, J. Kuskin, D. McCracken, W. McFarland, T. Meng, D. Nakahira, S. Ng, M. Rattehalli, J. Smith, R. Subramanian, J. S. Thomson, L. Thon, Y. Wang, R. Yu, X. Zhang Atheros Communications, Sunnyvale, CA

An 0.25 $\mu$ m CMOS mixed -signal baseband and MAC processor for the IEEE 802.11a WLAN standard in 0.25 $\mu$ m CMOS occupies 6.8 $\times$ 6.8mm <sup>2</sup> and contains 4.0M transistors in a 196-pin BGA package. Power consumption for transmit and receive is 326mW and 452mW. Additional data rates up to 108Mb/s are supported.

#### 7.3 A 10Gb/s and 40Gb/s Forward-Error-Correction Device for Optical Communications

9:30 AM

L. Song, M. Yu, M. Shaffer Agere Systems, Holmdel, NJ

Two forward error-correcting devices for OC-48/192/768 are implemented in 1.5V  $0.6\mu m$  CMOS. A 10Gb/s (or Quad2.5 Gb/s) device with 424k -gate Reed-Solomon core consumes 343mW. A 40Gb/s device contains 364k-gates and consumes 361mW.

BREAK 10:00 AM

## 7.4 IIR Digital Filter for ΔΣ Decimation, Channel Selection, and Square-Root-Raised-Cosine Nyquist Filtering

10:15 AM

*S. Mirabbasi, K. Martin* Univ. of Toronto, Toronto, Canada

A 1.8V 0.18µm CMOS  $\Delta\Sigma$  decimation filter also performs channel -selection and an approximate root-raised-cosine Nyquist pulse-shaping. The 0.1mm<sup>2</sup> IIR structure consumes 6.4mW (26.8mW) at 64MHz (240MHz) oversampling frequency.

#### 7.5 A 300MHz Quadrature Direct Digital Synthesizer/Mixer in 0.25µm CMOS

10:45 AM

*A. Torosyan<sup>1</sup>, A. Willson, Jr.*<sup>2</sup> UCLA, <sup>1</sup>Glendale/ <sup>2</sup>Los Angeles, CA

A 0.25µm quadrature direct digital frequency synthesi zer/mixer has 32b frequency control word, 0.07Hz tuning resolution, 12b inputs and 13b outputs offering 90.3dBc spurious-free dynamic range. The 4180 cell core occupies 0.36mm<sup>2</sup>. Power dissipation is <400mW at 300 MHz.

#### 7.6 Direct Digital Frequency Synthesizers using High-Order Polynomial Approximation

11:15 AM

D. De Caro, E. Napoli, A. G.M. Strollo Univ. of Napoli, Napoli, Italy

Two 80MHz 0.35 $\mu$ m 3.3V CMOS ROM -less DDFS using polynomial approximation are compared with Cordic-based circuits. A 60dBc SFDR DDFS uses 2nd-order polynomials and 0.18mm<sup>2</sup>, with 15mW dissipation. An 80dBc SFDR DDFS uses 3rd-order polynomials and 0.44mm<sup>2</sup>, with 35mW dissipation.

CONCLUSION 11:45 AM

#### HIGH SPEED TIMING

#### Chair: Stefanos Sidiropoulos, Aeluros Inc., Palo Alto, CA Associate Chair: Paul Landman, Texas Instruments, Dallas, TX

#### 8.1 Jitter Optimization Based on Phase-Locked-Loop Design Parameters

8:30 AM

*M. Mansuri, C-K Yang* Univ. of California, Los Angeles, CA

A tunable PLL allows independent optimization of loop parameters. The effects of varying PLL parameters (damping factor and bandwidth) on timing jitter is derived analytically and verified experimentally.

#### 8.2 A Self-Regulating VCO with Supply Sensitivity <0.15%delay/1%-supply

9:00 AM

*I. Hwang*<sup>1</sup>, S-*M. Kang*<sup>2</sup> <sup>1</sup>Univ. of Illinois at Urbana-Champaign, Urbana, IL <sup>2</sup>Univ. of California, Santa-Cruz, CA

A self-regulating VCO has supply sensitivity <0.15%-delay/1%-supply. The design uses a differential delay cell that contains an nMOS transmission gate for delay adjustment and a built-in feedback circuit for power-supply rejection. The charge-pump PLL embedded with this VCO has 40ps peak-to-peak jitter at 450MHz output with VCO at 900MHz.

#### 8.3 Low-Power Small-Area ±7.28ps Jitter 1GHz DLL-Based Clock Generator

9:30 AM

*C. Kim*<sup>1</sup>, *I. Hwang*<sup>2</sup>, S-*M. Kang*<sup>3</sup> <sup>1</sup>IBM, Austin, TX <sup>2</sup>Univ. of Illinois, Urbana, IL <sup>3</sup>Univ. of California, Santa Cruz, CA

A 1GHz DLL-based clock generator in 0.35µm CMOS occupies 0.08mm<sup>2</sup>. It has fast locking time and no jitter-accumulation problem. A phase detector with reset circuitry and a frequency multiplier overcome the limited locking range and frequency multiplication problem of conventional DLL-based systems. Measured peak-to-peak jitter is ±7.28ps.

#### BREAK 10:00 AM

#### 8.4 The Clock Distribution of the POWER4 Microprocessor 10:15 AM

*P. Restle*<sup>1</sup>, C. Carter<sup>2</sup>, J. Eckhardt<sup>3</sup>, B. Krauter<sup>2</sup>, B. McCredie<sup>2</sup>, *K. Jenkins*<sup>1</sup>, A. Weger<sup>1</sup>, A. Mule<sup>4</sup> <sup>1</sup>IBM, Yorktown Heights, NY/<sup>2</sup>Austin, TX/<sup>3</sup>Poughkeepsie, NY <sup>4</sup>Georgia Institute of Technology, Atlanta, GA

The clock distribution on the Power4 supplies a single critical 1.5GHz clock from one SOI-optimized PLL to 15,200 pins on a large chip with 20ps skew and 35ps jitter. The network contains 64 tuned trees driving a single grid, and specialized tools to achieve targets on schedule with no adjustment circuitry.

#### 8.5 The Core Clock System for a Next-Generation Itanium Processor

10:45 AM

*S. Wells*<sup>1</sup>, *F. Anderson*<sup>2</sup>, *E. Berta*<sup>1</sup> <sup>1</sup>HP, Fort Collins, CO <sup>2</sup>Intel, Fort Collins, CO

A PLL generates a high-frequency core clock for a 1GHz processor by multiplying up the system clock. The clock is distributed across the 19x14mm core via a shielded, balanced, H-tree to the final pulsed gated buffers with <62ps measured skew. Test features include phase shrinking and regional skew manipulation.

#### 8.6 A Low-Power RISC Microprocessor using Dual PLLs in a 0.13µm SOI Technology with Copper Interconnect and Low-k BEOL Dielectric

11:15 AM

S. Geissler, D. Appenzeller, E. Cohen, S. Charlebois, P. Kartschoke, P. McCormick, N. Rohrer, G. Salem, P. Sandon, B. Singer, T. Vonreyn, J. Zimmerman IBM, Essex Junction, VT

Microprocessors achieving clock frequencies >1GHz for mobile applications require solutions to maintain long battery life. Circuit and architecture solutions for dynamic frequency switching between multiple PLLs, DC power reduction methods, and impact of low-k dielectric on timing and power are discussed.

CONCLUSION 11:45 AM

#### DRAM AND FERROELECTRIC MEMORIES

#### Chair: Mark Bauer, Intel, Folsom, CA

Associate Chair: T. S. Jung, Samsung Electronics, Yongin, Kyungki, Korea

#### 9.1 Memory Design Using One-Transistor Gain Cell on SOI

8:30 AM

T. Ohsawa, K. Fujita, T. Higashi, Y. Iwata, T. Kajiyama, Y. Asao, K. Sunouchi Toshiba Corp., Yokohama, Japan

A 512kb DRAM has a  $7F^2$  one-transistor gain cell (F=0.18µm) on SOI. The array driving method makes selective write possible. Basic operation is verified by device simulation and hardware measurement. Simulations show 40ns access time. Non-destructive readout and Cb/Cs-free signal development improve cell efficiency.

#### 9.2 An Offset-Cancellation Bit-Line Sensing Scheme for Low-Voltage DRAM Applications

9:00 AM

S. Hong, S. H. Kim, S. J. Kim, J. Wee, J. Chung Hynix Semiconductor Inc., Ichon, Korea

Offset-cancellation provides low-voltage DRAM operation. The offset cancelling bit-line sense amplifers are pitch-matched to the conventional 0.16µm DRAM cell array without process modifications. Results indicate better refresh characteristics than conventional bit-line sense amplifiers even at 1.5V.

#### 9.3 A 300MHz Multi-Banked eDRAM Macro Featuring GND Sense Bit-Line Twisting and Direct Reference-Cell Write

9:30 AM

*J. Barth, D. Anand, J. Dreibelbis, E. Nelson* IBM, Essex Junction, VT

A 0.12µm growable eDRAM macro has GND sense, bit -line twisting, direct reference cell write, a flexible multi-banking protocol, and column redundancy to support multi-banking. The protocol supports simultaneous activate, read/write and pre-charge to three different banks. Hardware measurements verify 300MHz operation, 6.6ns tacc, and 10ns trc.

#### BREAK 10:00 AM

#### 9.4 A Hierarchy Bitline-Boost Scheme for Sub-1.5V Operation and Short Precharge Time on High-Density FeRAM 10:15 AM

H-B. Kang, H-W. Kye, G-I. Lee, J-H. Park, J-H. Kim, S-S. Lee, S-K. Hong, Y-J. Park, J-Y. Chung Hynix Semiconductor Inc., Ichon, Korea

This work develops three concepts: low-voltage operation with boost voltage control of bitline and plateline, reduced bitline capacitance with multiple divided sub cell array, and increased chip performance with write operation sharing both active and precharge time period. A 256kb test chip with  $3.0x1.0\mu$ m<sup>2</sup> 1T1C memory cells in 0.25µm desig n roles is expected to achieve 180ns access and 70ns precharge at 1.5V based on internal probing.

#### 9.5 A Quasi-Matrix Ferroelectric Memory for Future Silicon Storage

10:45 AM

*T. Nishihara, Y. Ito* Sony Corp., Kanagawa, Japan

A memory unit consists of multiple ferroelectric capacitors that store individual bits and share one access transistor. Disturb degradation and cross-talk effects are suppressed to an acceptable level. The capacitors can be multi-stacked, increasing packing density by a number of times.

## 9.6 A 0.25µm 3.0V 1T1C 32Mb Nonvolatile Ferroelectric RAM with ATD and CFLSA

11:15 AM

M-K. Choi, B-G. Jeon, N. Jang, B-J. Min, Y-J. Song, S-Y. Lee, H-H. Kim, D-J. Jung, H-J. Joo, K. Kim Samsung Electronics, Yongin-City, Korea

A nonvolatile 32Mb ferroelectric random-access memory with  $0.25\mu m$  design rules uses ATD control for SRAM applications and a commonplate folded bit-line cell scheme with current forcing latched sense amp for low noise level without cell area penalty.

CONCLUSION 11:45 AM

#### HIGH-SPEED ANALOG-TO-DIGITAL CONVERTERS

#### Chair: Venu Gopinathan, Broadcom Corp. Associate Chair: K. Nagaraj, Texas Instruments

#### 10.1 A 4GSample/s 8b ADC in 0.35µm CMOS

8:30 AM

*K. Poulton<sup>1</sup>, R. Neff<sup>1</sup>, A.Muto<sup>1</sup>, W. Liu<sup>1</sup>, A. Burstein<sup>2</sup>, M. Heshami<sup>3</sup>* <sup>1</sup>Agilent Technologies, Palo Alto, CA <sup>2</sup>Volterra, Fremont, CA <sup>3</sup>Virata, Cupertino, CA

A 4GSample/s 8b ADC in 0.35µm CMOS achieves accuracy of 7 effective bits at DC and 6.1 effective bits for 1GHz input, while dissipating 4.6W. It uses 32 current-mode pipelines driven by 32 interleaved clocks with 1.1ps rms accuracy.

#### 10.2 A 6b 1.6GSample/s Flash ADC in 0.18µm CMOS Using Averaging Termination

9:00 AM

*P. Scholtens, M. Vertregt* Philips, Eindhoven, The Netherlands

A 1.6GSample/s 6b flash analog-to-digital converter in 0.18µm CMOS for storage read channels is described. The array of amplifiers and averaging resistors is terminated with less overrange while maintaining full-scale linearity. Consuming 340mW, it achieves 5.7 effective bits at DC and 5 effective bits at 660MHz.

#### 10.3 A 7b 450MSample/s 50mW CMOS ADC in 0.3mm<sup>2</sup>

9:30 AM

K. Sushihara, A. Matsuzawa Matsushita Electric Industrial Co., Osaka, Japan

A 7b 450MSample/s CMOS ADC in 0.18µm technology is used for the embedded digital read channel system in DVD SOC. A dynamic comparator and an interpolation circuit composed with gate-width-weighted transistors consumes 50mW and occupies 0.3mm<sup>2</sup>.

BREAK 10:00 AM

#### 10.4 A 10b 120MSample/s Time-Interleaved Analog-to-Digital Converter with Digital Background Calibration

10:15 AM

S. Jamal<sup>1</sup>, D. Fu<sup>2</sup>, P. Hurst<sup>3</sup>, S. Lewis<sup>3</sup> <sup>1</sup>Marvell Semiconductor Inc., Sunnyvale, CA <sup>2</sup>Maxim Integrated Products, Sunnyvale, CA <sup>3</sup>Univ. of California at Davis, Davis, CA

Digital calibration using adaptive signal processing corrects offset mismatch, gain mismatch, and sample-time error between timeinterleaved channels in a 10b 120MSample/s pipelined ADC. With background calibration, peak SNDR is 56.8dB and power dissipation is 234mW from 3.3V. Active area is 12.5mm<sup>2</sup> in 0.35µm CMOS.