# **ADVANCE PROGRAM**

2003

IEEE

INTERNATIONAL

SOLID-STATE

CIRCUITS

CONFERENCE

FEBRUARY 9, 10, 11, 12, 13

CONFERENCE THEME:

POWER-AWARE

SYSTEMS

SAN FRANCISCO MARRIOTT HOTEL Analog Telecom: Near-Limit CMOS:

5-DAY ROGRAM

#### ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-ona-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and application to maintain technical currency, and to network with leading experts.

CONFERENCE HIGHLIGHTS

2003 is the 50th Anniversary of ISSCC. This year, several special events are planned to celebrate the 50th anniversary including: a plenary presentation by Gordon Moore on the past present and future of integrated circuits; a historical exhibit of key milestones in solid-state circuits; a livinghistory video of key contributors to IC technology; a 50th-Anniversary Social Hour; and a 50th Anniversary Edition of the JSSCC / ISSCC DVD free to ISSCC registrants.

On Sunday, February 9, the day before the official opening of the Conference, ISSCC 2003 offers:

A choice of up to 3 of a total of 7 Tutorials

An ISSCC Workshop on Analog Telecom Access Circuits and Concepts (ATACC), which will address optical and electrical backplane transceivers.

An SSCTC Workshop on Implications of Near-Limit CMOS on Circuits and Applications

On Sunday evening, three special-topic evening sessions addressing next-generation circuit-design challenges will be offered starting at 7:30 PM:

How Far Can Integration Go for 3G Cellphones

Circuits in Emerging Technologies

Highlights of DAC (in which some of the best circuit-design-related papers from the Design-Automation Conference are presented for İSSCC attendees)

These sessions offer leading experts in the field presenting tutorial background and state-of-the-art design strategies in a workshop format, and

are open to all attendees.

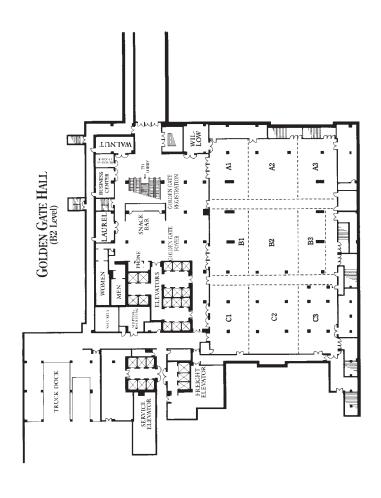

On Monday, February 10th, ISSCC 2003 offers three plenary papers followed by technical sessions. There will be a special 50th-Anniversary Social Hour for all attendees, from 5:15 to 6:30 in Golden-Gate Hall. Evening panels will be held on Monday and Tuesday evenings from 8:00PM to 10:00PM.

On Thursday, February 11th, ISSCC 2003 offers a choice of three events:

• An ISSCC Short Course: System-On-A-Chip Design. Three ses-

sions of the Short Course will be offered, with staggered starting times that will be filled on a first-come, first-served basis

An ISSCC Microprocessor-Design Workshop: Microprocessor Design

in the Power-Constrained Era

An ISSCC Workshop on Gigahertz Radio Front Ends (GIRAFE)

Use of the ISSCC web-registration site (www.isscc.org) is strongly encouraged. You will be provided with immediate confirmation on registration for tutorials, workshops and the Short Course.

CONFERENCE INFORMATION

The coordinated timing of papers given at ISSCC permits attendees to session-hop from session to session, without having to miss any important material. This Advance Program provides you with the starting time for each paper. Taking of pictures and videos during sessions is not permitted.

A printed Supplement with speakers' visuals will be sent to all registered attendees within one month of the conclusion of ISSCC 2003. A CDROM containing both the ISSCC 2003 Digest of Technical Papers and the Visuals Supplement will be mailed in late Spring to speakers and all attendees paying the member or non-member Conference-registration fee.

**Conference Information:** Courtesy Associates; Phone: 202-973-8667;

Fax: 202-973-8722; email: isscc@courtesyassoc.com

Press Information: Kenneth C. Smith, University of Toronto Phone: 416-978-5033; Fax: 416-971-2286; email: lcfujino@cs.com Registration: Event Solutions Unlimited, P.O. Box 32862, Baltimore, MD 21282; Phone: 410-559-2236 or 1-800-937-8728;

Fax: 410-559-2217; email: issccinfo@yesevents.com

ISSCC Website: www.isscc.org

Make the most of your trip to San Francisco! Visit the San Francisco

Convention & Visitors Bureau Website at <a href="www.sfvisitor.org">www.sfvisitor.org</a>. ISSCC 2003 is sponsored by the IEEE Solid-State Circuits Society. Co-sponsors are the IEEE San Francisco Section and Bay Area Council, and the University of Pennsylvania.

### **CONTENTS**

| Tutorials                      |                                                               |  |  |

|--------------------------------|---------------------------------------------------------------|--|--|

| W1                             | ATACC Workshop                                                |  |  |

| W2                             | SSCTC Workshop                                                |  |  |

|                                | SPECIAL-TOPIC EVENING SESSIONS                                |  |  |

| SE1                            | Highlights of DAC                                             |  |  |

|                                | Circuits in Emerging Technologies                             |  |  |

| SF3                            | How Far Can Integration Go For 3G Cellphones?                 |  |  |

|                                | PAPER SESSIONS                                                |  |  |

| 1                              | Plenary Session                                               |  |  |

| 2                              | Multimedia Signal Processing                                  |  |  |

| 3                              | Oversampled A/D Converters                                    |  |  |

| 4                              | Clock Recovery and Backplane Transceivers22-23                |  |  |

| 5                              | Wireless PAN Transceivers                                     |  |  |

| 6                              | Low-Power Digital Techniques                                  |  |  |

| •                              | DISCUSSION SESSIONS                                           |  |  |

| E1                             | Analog IP — Stairway to SoC Heaven?                           |  |  |

| E2                             | Will MEMS, Imagers, and Displays Be Key to the                |  |  |

|                                | Growth of the IC Industry?                                    |  |  |

| E3                             | Good, Bad, Ugly — 50 Years of Memory Evolution. What Next? 28 |  |  |

|                                | PAPER SESSIONS                                                |  |  |

| 7                              | DACs and AMPs                                                 |  |  |

| 8                              | Communication Signal Processing                               |  |  |

| 9                              | TD: Digital Architecture and Systems34-35                     |  |  |

| 10                             | High Speed Building Blocks                                    |  |  |

| 11                             | Microsensors and BioMEMs                                      |  |  |

| 12                             | CMOS Imagers, Sensors and Displays                            |  |  |

| 13                             | 40Gb/s Communication ICs                                      |  |  |

| 14                             | Microprocessors                                               |  |  |

|                                | Ference Timetable                                             |  |  |

| Reai                           | stration and Hotel Reservation Forms                          |  |  |

| 15                             | Cellular Communications                                       |  |  |

| 16                             | Non-Volatile Memory                                           |  |  |

|                                | DISCUSSION SESSIONS                                           |  |  |

| E4                             | Future Mobile Phones: A Beautiful Dream or                    |  |  |

|                                | Smoke in LSI Technology?                                      |  |  |

| E5                             | Fineline Prototyping: Breaking New Ground                     |  |  |

|                                | or Breaking the Bank?                                         |  |  |

| E6                             | SoC: DOA? RIP?                                                |  |  |

|                                | PAPER SESSIONS                                                |  |  |

| 17                             | SRAM and DRAM54-55                                            |  |  |

| 18                             | Nyquist A/D Converters56-57                                   |  |  |

| 19                             | Processor Building Blocks                                     |  |  |

| 20                             | Wireless Local Area Networking60-61                           |  |  |

| 21                             | TD: Organic and Nanoscale Technologies                        |  |  |

| 22                             | TD: Embedded Technologies                                     |  |  |

| 23                             | Mixed-Signal and Wireless Techniques                          |  |  |

| 24                             | Clock Generation                                              |  |  |

| 25                             | RF Infotainment                                               |  |  |

| 26                             | Embedded Memory and Digital Systems72-73                      |  |  |

| Shor                           | t Course: System-on-a-Chip                                    |  |  |

| WORKSHOPS                      |                                                               |  |  |

| W3                             | Microprocessor-Design Workshop                                |  |  |

| W4                             | GIRAFE Workshop                                               |  |  |

|                                | mation                                                        |  |  |

| Committees                     |                                                               |  |  |

|                                | l Layout                                                      |  |  |

|                                | <b>s</b>                                                      |  |  |

| <b>50th-Anniversary Events</b> |                                                               |  |  |

### **TUTORIALS**

### T1: Basics of Serial Backplane Transceivers

This tutorial covers basic elements of the design of multi-gigabit-per-second serial transceivers for use in backplane applications. Sources of signal impairment, such as dielectric losses, reflections at connectors, crosstalk, and package limitations will be addressed. Channel modeling and measurement techniques will also be presented. Modulation and equalization techniques to overcome the bandwidth limitations will be covered, as well as practical considerations for the integration of multiple channels onto a large digital ASIC. An overview of clock-and-data-recovery circuits will be presented, and first-order circuit designs will be discussed. Finally, all aspects of the design of a serial transceiver will be reviewed in the context of a real-world example.

Instructor: Aaron Buchwald was born in Ames, IA, in 1960. He received the BSEE degree from the University of Iowa in 1982, and the MS and Ph.D degrees in electrical engineering from the University of California, Los Angeles, in 1984 and 1993, respectively. He has worked for Hughes Aircraft in El Segundo, CA, and Siemens in Munich, Germany. He was an Assistant Professor at The Hong Kong University of Science and Technology, and since 1994 has been with Broadcom Corporation in Irvine, CA.

### T2: Design For Test and Debug

This tutorial is targeted towards the impact of design for test and debug on micro-architectural and circuit implementations. It will begin with review of failure mechanisms on chip, fault modeling, and Automatic Test Pattern Generation (ATPG). Then an overview of initial chip bring-up and qualification procedures will be presented, followed by scan methodologies and specific implementations of scan for latches and flip-flops; BIST for memory structures and regular logic; BISR and redundancy techniques for memory; An overview of JTAG interface; Implementation of on-chip logic analyzers and clock compression for debugging; Current and advanced chip probing techniques and FIB repair. Included, as well, will be discussion of various other test/debug techniques.

Instructor: Shannon Morton is a Chief Engineer in SGI's high-end MIPS microprocessor design team in Boston, MA, where he is the implementation leader for the L2 cache. In 1991, he graduated from the University of Adelaide, Australia, with a BE in electrical and electronic engineering, and again in 1996, with a Ph.D in asynchronous systems. From 1997 to 2001, he was a Principal Engineer at DEC/Compaq with the Alpha Microprocessor Design Team, where he contributed to the implementation of EV7. He lead the L2 cache design for EV8, working closely with the test group on various test/debug features such as BIST/BISR for memories, JTAG interfaces, OCLA, and clock compression. His interests include signal integrity, advanced circuits and technologies, and design for productivity.

#### T3: Introduction to BioMEMS

BioMEMS integrates microscale sensors, actuators, microfluidics, microoptics, and structural elements with computation, communications, and controls. This tutorial presents an introduction to BioMEMS technology and its application to bioanalytical, surgical, and therapeutic microsystems with special emphasis on opportunity directions for the circuit designer. Basic concepts in biology needed to understand biochips will also be presented.

Instructor: Dennis Polla currently serves as President and CEO of the SurroMed Institute of Nanobiotechnology in Singapore. He has previously held faculty positions at Yale University and the University of Minnesota where he served as Director of the Biomedical Engineering Institute, Professor of Electrical Engineering, and Chairman of the Department of Biomedical Engineering. Dr. Polla studied electrical engineering at MIT and completed his Ph.D in MEMS at U.C. Berkeley.

### T4: MRAM Technology & Circuits

Magnetoresistive Random-Access Memory (MRAM) technology is approaching manufacturing status. It promises the density and read-andwrite performance of DRAM with the nonvolatility of hard-disk drives, but without the write-fatigue problems of EEPROMs or flash memory. This tutorial describes the fundamentals of MRAM technology starting with magnetoresistance and concentrating predominantly on Giant MagnetoResistance and Tunneling Magnetoresistance. Cell designs include the Pseudo-Spin Valve (PSV) and the Magnetic Tunnel Junction (MTJ) cell. Briefly described are the unique processes used for fabricating MRAMs and how these processes result in on-chip integration with circuits. The most common chip architectures for reading and writing data are described. Emphasis is placed on the MTJ cell because it appears to be closest to production. The basic properties of the MTJ cell lead to circuit-design constraints. The voltage across the tunnel junction is limited due to the thin dielectric used. Tunneling resistance is likely to have a wide tolerance due to its exponential dependence on dielectric thickness. Circuit challenges related to sensing data from the MTJ cell are discussed. Writing MTJ cells requires currents in two orthogonal lines, and relatively tight tolerances must be maintained in order for all cells in the memory array to operate properly. Finally, some challenges for future MRAM designs are identified, and some potential solutions to these challenges are discussed.

Instructor: James Daughton is Chief Technical Officer and a board member of NVE Corporation, which he founded in 1989. NVE specializes in products combining integrated circuits with advanced magnetic materials. Before founding NVE, Dr. Daughton spent over 15 years at Honeywell, managing solid-state research and development. Before that, he spent 10 years at IBM in Yorktown Heights and Burlington, working on magnetic and semiconductor memory devices. He received his BS, MS, and Ph. D degrees in electrical engineering in 1959, 1961, and 1963, respectively, from Iowa State University. He is a fellow of the IEEE, a member of the Magnetics Society, and an adjunct professor of physics at the University of Minnesota. He has published over 65 papers and has 19 issued patents, primarily dealing with thin magnetic films and devices. In 1994, Dr. Daughton was a Distinguished Lecturer for the Magnetics Society of the IEEE.

### **TUTORIALS**

### T5: Wireless LAN: Architectures and Design

An overview of competing wireless LAN architectures in the 2.4GHz and 5.0GHz spectra is presented. RF and analog requirements will be discussed. A detailed discussion of competing modem algorithms (OFDM, QAM, QPSK, CCK, etc.) will be presented, with advantages and disadvantages identified for each. Filtering requirements and some aspects of the software protocol stack will be compared. The tutorial will end with some implementation ideas for the harder issues, and a performance analysis for each system.

Instructor: David Shoemaker is VP of Engineering at Engim, in Acton, MA. Engim is a start-up focused on high-performance communications, currently targeted at Wireless LAN. David leads efforts in RF, analog, digital, and software systems at Engim, and is currently working on a 600Mb/s access point for wireless LAN. Previously, David was CTO for the Internet Infrastructure Business Unit at Texas Instruments, focusing on high performance network processing interfaces. David received his Ph.D, SM, and SB from MIT.

### T6: Highly Integrated RF and Wirelss Transceivers

This tutorial provides an introduction to the challenges associated with highly-integrated RF and wireless transceivers. Both system-level and circuit-level challenges are addressed. The focus is on transceivers for high-data-rate systems such as EDGE, WCDMA, and 802.11, which require linearity in both the TX and RX paths. Some of the topics that will be addressed are architectures such as direct-conversion RX and TX which enable elimination of external components, circuit-level issues associated with implementing these architectures, the impact of finite isolation, and manufacturability.

Instructor: Tony Montalvo received his BS in Physics from Loyola University in 1985, his MSEE from Columbia University in 1987 and his Ph. D in electrical engineering from North Carolina State University in 1995. From 1987 to 1991, he was a flash-memory designer with AMD. From 1995 to 2000 he was with Ericsson in Research Triangle Park, NC, where he was the manager of the RF and Analog IC group. Since 2000, he has been the Director of the Analog Devices Raleigh Design Center. He is also an Adjunct Professor at North Carolina State University where he was named Outstanding Teacher in 1995. He holds 14 patents and has authored or co-authored 8 papers.

### Sunday, February 9th 8:00 AM

### T7: DSL Splitters and Drivers

This tutorial will start with a general introduction to ADSL. The signal characteristics will be described with discussion on DMT-modulation, power level, crest factor, etc. Further along in the tutorial, the architecture of an ADSL analog front end will be shown emphasizing the design for performance. Some design, architecture and integration considerations will be reviewed. Attention will be given to the hybrid function showing the impact of the echo path. Line-driver characteristics and requirements, such as linearity and power dissipation, will be handled. Because of their importance, several classes/topologies of line drivers will be highlighted, with emphasis on their power dissipation. The issues of further density increase and possible solutions will be discussed. Finally, the POTS splitter function and its restrictions will be examined while looking for the possibilities for integration. The tutorial will end with an examination of the possibilities for the further evolution of ADSL towards higher bandwidth and more flexibility.

Instructor: Elve D. J. Moons was born in 1959 in Kermt, Belgium. He graduated from the Katholieke Universiteit Leuven in 1982, where he received a degree in electronic engineering. In the same year, he joined the microelectronics design group within Alcatel Bell in Antwerp, Belgium. There, he was active in the integration of telecommunication circuits, especially in the development of several generations of subscriber-line interface circuits. In the beginning he was a designer and later became ASIC team leader. For the past few years he has been involved in the development of ADSL analog front-end components while managing the analog ASIC design team within Alcatel in Antwerp, Belgium.

### ATACC WORKSHOP

W1: Analog Telecom and Circuit Concepts

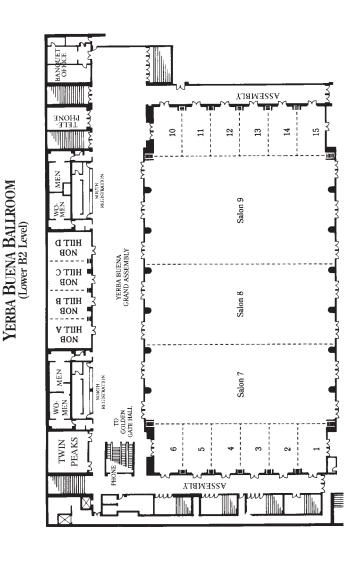

(Salon 7)

Organizer/Chair: Jan Sevenhans, Alcatel BND

Committee:

David Allstot, University of Washington, Seattle, WA

Russell Apfel, Legerity, Austin, TX

Franz Dielacher, Infineon Technology Austria, Villach, Austria

Kunihiko lizuka, Sharp, Tenri-shi, Japan

Tetsuro Itakura, Toshiba, Kawasaki-shi, Japan

John Long, Delft University of Technology,

Mekelweg, The Netherlands

Bram Nauta, University of Twente, Enschede, The Netherlands

Jan Sevenhans, Alcatel BND, Antwerp, Belgium

Trudy Stetzler, Texas Instruments, Stafford, TX

Hirotaka Tamura, Fujitsu Laboratories, Kawasaki-shi, Japan

Photons and electrons are competing to capture the backplane transceiver market in the next few years. Optical backplanes are coming, and integrated optics are in line as the next step. But electrical interconnect in the gigahertz range is the current bread and butter technology. Broadband Telecom is pushing this technology towards its natural limits, and will continue to do so in the next few years. Voltage-mode and current-mode I/O drivers and receivers are still driving electrons back and forth over the copper connections in the rack and in the PCBs of routers and gigahertz link equipment. Probably at some point, photons will take over this job and become the messengers for terabit connections.

This Workshop will challenge the experts in electrical and optical transceivers from the electrical or fibre optical interface circuits to the digital synchronisers for data recovery and system interface building blocks. It is a full day dedicated to the strongest technologies and circuits. Electrons and photons will exercise the minds of the speakers and the experts in the audience during the eight presentations and also in the concluding panel discussion.

Lunch and breaks are included in the registration fee. The workshop begins at 8:30 AM and ends at approximately 5:30 PM. If the workshop is full, the registering attendee will not be charged, or will be reimbursed after the Conference if a check was submitted.

### Sunday, February 9<sup>th</sup> 8:30 AM

### **Workshop Program**

| <u>Time</u> | Topics                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------|

| 8:00        | BREAKFAST                                                                                              |

| 8:30        | Welcome<br>Jan Sevenhans, Alcatel BND                                                                  |

| 8:40        | Electrical Backplane Interconnects to 12Gb/s and Beyond John T. Stonick, <i>Accelerant</i>             |

| 9:25        | Optical Backplanes-Fact or Fiction? D. V. Plant, Photonics                                             |

| 10:10       | COFFEE BREAK                                                                                           |

| 10:25       | Integrated Electrical Backplane Transceivers Kimo Tam, Analog Devices                                  |

| 11:10       | High-Data-Bandwidth Transceivers for Multi-Channel<br>Serial Data<br>Muneo Fukaishi, <i>NEC</i>        |

| 11:55       | The Future of Electrical Backplanes: High-Speed at Low-Cost Gerrit den Besten, Philips                 |

| 12:40       | LUNCH                                                                                                  |

| 1:40        | Electrical Interconnect for Backplanes<br>and Short (<30m) Cables<br>Takeshi Horie, Fujitsu            |

| 2:25        | Transponders and Transceivers for Serial and Parallel<br>Optical Links<br>Michael Neuhaeuser, Infineon |

| 3:10        | CMOS Capabilities for Electrical Backplane Transceivers<br>Andy Joy, Texas Instruments                 |

| 3:55        | PANEL DISCUSSION                                                                                       |

| 4:40        | Conclusion                                                                                             |

### SSCTC WORKSHOP

W2: Implications of Near-Limit CMOS on Circuits and Applications

(Golden Gate B2/B3)

Organizers: Tak Ning, IBM Research

Stan Schuster, IBM Research

While technologists continue to provide us with ever-faster CMOS devices, it is clear that these fast devices have properties that were not seen in CMOS just a few years ago. From the perspective of circuits and applications, these unexpected properties are mostly detrimental, resulting in increasing challenges to circuits and systems designers. From the technologists' perspective, we are approaching the limits of scaled CMOS. Scaling degrades device characteristics challenging the circuits designer.

This workshop provides an open forum for discussions of the implications of evolving CMOS, near its limits, on circuits and applications. Invited speakers will lead off discussion on issues related to:

- CMOS near its scaling limits, status and future prospects

- Power and power density, issues at the chip and system levels

- Reliability, issues such as burn-in, soft error, error correction, etc.

- Gate current, its limits and effects on circuits

- Low-power designs, their benefits and potential pitfalls

### Sunday, February 9<sup>th</sup> 8:30 AM

### **Workshop Program**

| <u>Time</u> | <u>Topics</u>                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| 8:00        | BREAKFAST                                                                                                       |

| 8:30        | Welcome and Introduction                                                                                        |

| 8:40        | Challenges Near the Limits of CMOS Scaling<br>Yuan Taur, University of California, San Diego, CA                |

| 9:20        | Low-Power Technologies in the Near-Limit CMOS Regime Kazuo Yano, <i>Hitachi, Tokyo, Japan</i>                   |

| 10:00       | COFFEE BREAK                                                                                                    |

| 10:30       | Infant-Mortality Control by Burn-In and by Design<br>Shirley Glenn, Intel, Hillsboro, OR                        |

| 11:10       | Transistor and BEOL Tradeoffs in Near-Limit  CMOS Technology  Rich Klein, Advanced Micro Devices, Sunnyvale, CA |

| 11:50       | LUNCH                                                                                                           |

| 1:00        | Effects of Gate Tunneling in Near-Limit CMOS Circuits<br>Hisham Massoud, Duke University, Durham, NC            |

| 1:40        | Low-Power Challenges for Digital CMOS Beyond 90nm<br>Shekhar Borkar, Intel, Hillsboro, OR                       |

| 2:20        | BREAK                                                                                                           |

| 2:50        | Design, Process and Environmental Contributors to<br>Delay Variation<br>Kerry Bernstein, IBM, Burlington, VT    |

| 3:30        | Talk title TBD  Rob Rutenbar, Carnegie Mellon University, Pittsburgh, PA                                        |

| 4:10        | Conclusion                                                                                                      |

### SPECIAL-TOPIC EVENING SESSIONS

SE1: Highlights of DAC

(Salon 7)

Organizer/Chair: Steve Molloy, Chief Architect,

Netergy Microelectronics, Santa Clara, CA

Session Co-Chair: Joseph Williams, Distinguished Member of

Technical Staff, Agere Systems, Holmdel, NJ

This special session contains four excellent presentations from the Design Automation Conference (DAC) held in June 2002. Each year DAC covers the latest in design methodologies and EDA tool developments, with a strong level of participation from both industry and academia. The four presentations in this session cover a variety of representative topics, including design methodology, analog and digital simulation techniques, and recent advancements in model development.

As designs become more and more complex, design-time windows are also becoming shorter. This creates an interesting challenge: to achieve fully-operational first silicon for designs of incredible complexity. The first presentation describes design methodologies and CAD-tool requirements for advanced 10MGate SoC design in the context of several large design examples.

The second presentation is by a DAC Best Paper Award winner, and describes a novel technique for mixing compiled-code and interpreted-code approaches to instruction-set simulation. Compiled-code simulators traditionally have the advantage of higher speed, though this comes with many restrictions including a requirement for static program code. This presentation demonstrates high performance with fewer restrictions using a just-in-time compilation technique. The approach is described in the context of several real-world processors including the ARM7 and ST200.

Frequency synthesizers are critical components in many important system-design areas such as wireless communications. Simulation places demanding requirements on both accuracy and simulation speed. The third presentation describes new simulation techniques for fractional-N synthesizers, and their application to a variety of circuits. The proposed techniques are shown to match closely with measured results, and are widely applicable to a variety of simulation frameworks.

In the past, it has been shown that the sizing of transistor-level analog and mixed-signal integrated circuits can be formulated as a geometric program. A particularly time-consuming and computationally expensive step in this process has always been the generation of analog performance models. The final presentation of the session describes design-automation techniques for generating high-quality analog performance models, replacing what, in the past, has been a manual process. The techniques are based on a new direct-fitting approach that efficiently fits model templates to numerical data from SPICE simulations.

### Sunday, February 9th 7:30 PM

SE1: Highlights of DAC

Time Topics

7:30 Challenges in Achieving First-Silicon Success for 10MGate SoCs: A Silicon Engineering Perspective Aurangzeb Khan, Corporate Vice President/General Manager, Cadence Design Systems, Sunnyvale, CA

8:00 A Universal Technique for Fast and Flexible Instruction-Set Architecture Simulation

Achim Nohl, Aachen University of Technology,

Aachen, Germany

8:30 Fast and Accurate Behavioral Simulation of Fractional-N

Frequency Synthesizers and other PLL/DLL Circuits

Michael H. Perrott, Assistant Professor,

Massachusetts Institute of Technology, Cambridge, MA

9:00 An Efficient Optimization-Based Technique to Generate Posynomial Performance Models for Analog Integrated Circuits

> **Walter P. Daems,** Katholieke Universiteit, Leuven, Belgium

**Georges Gielen**, *Katholieke Universiteit, Leuven, Belgium*

Willy Sansen, Katholieke Universiteit, Leuven, Belgium

### SPECIAL-TOPIC EVENING SESSIONS

SE2: Circuits in Emerging Technologies

(Salon 8)

Organizer: Werner Simbuerger, Infineon, Corporate Research,

Munich, Germany

Chair: lan Young, Intel, Logic Technology Development,

Hillsboro, OR

Ubiquitous access to information, anywhere, anyplace, and anytime, will require whole new kinds of information systems. This demand for novel communication systems will translate into innovation in emerging technologies, circuit-design methodologies and fabrication techniques. At the core of these approaches, heavy emphasis is placed on finding the right match between circuit techniques and fabrication-process technology.

This Special-Topic Evening Session addresses circuit techniques that are emerging for both high-performance design at microwave frequencies and for future giga-scale integrated circuits. Some of these techniques include high-speed CMOS, SiGe, GaAs and InP, double-gate FinFET, and Carbon Nanotube technologies.

Recently, CMOS has been demonstrated to be a viable technology for very-high-bit-rate broadband circuit design at over 10Gb/s in highly integrated systems.

Meanwhile, advances in device scaling and doping-profile optimization have also resulted in SiGe bipolar transistors with impressive performance, including cut-off frequencies in the range of 200GHz. This makes them an attractive choice for applications at 40Gb/s and above.

Current InP bipolar integrated-circuits support high-performance mixedsignal applications at frequencies up to 200GHz. The high cut-off frequencies and high breakdown voltages present a unique combination which addresses some major issues.

With the scaling of device dimensions being the primary factor driving improvements in integrated circuit performance and cost, new device structures, such as FinFET, and new materials will be needed to overcome the technological challenges.

Finally, nanometer-scale electronic devices will not only be much smaller, but they must also operate according to designs and quantum-mechanical principles that are quite different from those employed by present-day microelectronic devices.

The speakers will present circuits and circuit techniques in these emerging technologies. In addition, they will address potential solutions for overcoming emerging challenges.

| 111110 | Τορίοσ                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7:30   | CMOS High-Speed Broadband Techniques Michael Green, Professor, University of California, Irvine, CA                                      |

| 8:00   | Design of SiGe Bipolar Circuits for 40°Gb/s Applications<br>Herbert Knapp, Infineon Technologies,<br>Corporate Research, Munich, Germany |

| 8:30   | Indium-Phosphide Bipolar Integrated Circuits: 40GHz and Beyond Mark Rodwell, Professor, University of California, Santa Barbara, CA      |

| 9:00   | The Double-Gate FinFET: Device Impact on Circuit Design<br>Ingo Aller, IBM Entwicklung GmbH,<br>Boeblingen, Germany                      |

| 9:15   | Carbon Nanotubes: From Synthesis to Integration<br>Hongjie Dai, Associate Professor, Stanford                                            |

University, CA

Time

Tonics

### Sunday, February 9th 7:30 PM

SE3: How Far Can Integration Go For 3G Cellphones?

(Salon 9)

Organizer: William O. Camp, Jr., Senior Scientist, Sony Ericsson

Mobile Communications, Research Triangle Park, NC

Chair: Trudy Stetzler, Senior Member of the Technical Staff,

Texas Instruments, Stafford, TX

This special-topic session will use a 3G Cellular Phone as an example of the integration that should be possible in the near future for such devices. The first talk discusses the trends in cellular-phone integration and the architectural tradeoffs that must be made as further integration occurs. It will be shown that the requirements on these phones are increasing with each new standard as well as by the requirement for increased functionality that is expected by the user.

The second and third talks then discuss the baseband and RF sections of a cellular phone. The challenges to increased integration in each of these sections are discussed. Architectural options and tradeoffs are reviewed, and trends in each of these areas are demonstrated.

The last talk reviews these architectural tradeoffs in light of technology advances that might be expected to occur in the near- to mid-term time frame. Technological advances that are required to permit further integration with a simultaneous increase in performance are discussed.

Time

**Topics**

| 7:30 | System Requirements and Integration Trends Sven Mattisson, Expert, Analog System Design, Ericsson, Lund, Sweden                    |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| 8:00 | Integration of Analog, Digital and Power Regulation on a Chip James Mielke, Director Systems and Architecture, Motorola, Tempe, AZ |

| 8:30 | Advanced RF Integration William Krenik, Wireless Advanced Architectures Manager, Texas Instruments, Dallas, TX                     |

9:00 Challenges and Future Trends

John Long, Professor, Delft University of

Technology, Delft, The Netherlands

### SESSION 1 SALON 7-9

### PLENARY SESSION -- INVITED PAPERS

Chair: Tim Tredwell, Eastman Kodak Research Labs,

Rochester, NY

ISSCC Executive-Committee Chair

Associate Chair: Anantha Chandrakasan, Massachusetts Institute

of Technology, Cambridge, MA ISSCC Program-Committee Chair

#### FORMAL OPENING OF CONFERENCE

8:30 AM

1.1 No Exponential Is Forever: But "Forever" Can Be Delayed! 8:40 AM

Gordon E. Moore Intel (Retired)

By any measure, the semiconductor industry has experienced fantastic growth over the last 50 years. Starting from nothing, it has now passed \$200 billion in annual revenue and has become the foundation of a trillion-dollar electronics industry. This unprecedented growth is the result of the combination of a unique technology and an extremely elastic market. Over this brief history, many parameters relating to the industry have changed approximately exponentially with time. These include chip complexity, chip performance, feature size, and the numbers of transistors produced each year. This talk will explore some of these trends, and will look at the current status of silicon technology, and at challenges going forward.

ISSCC, SSCS, JSSC, & IEEE AWARD PRESENTATIONS

9:30 AM

**BREAK 10:00 AM**

### Monday, February 10th 8:30 AM

### 1.2 Perspectives on Power-Aware Electronics

10:15 AM

Takayasu Sakurai University of Tokyo, Tokyo, Japan

In the coming ubiquitous IT society, low-power design is one of the key features at which the VLSI designer should aim. Otherwise, power increase will remain as one of the main obstacles to Moore's law growth. Unless VLSI power is lowered by orders of magnitude, we cannot enjoy the progress that scaling offers.

This talk will cover what we now have, and what we should provide in our low-power armory to allow us to cope with ever-increasing leakage loss, as well as dynamic power. The techniques to be presented range over the system, software, circuit, and device level including interconnect and I/O issues. The novel trend is to examine cooperative approaches between levels such as software-circuit cooperation and circuit-technology cooperation.

The biggest challenge that System-on-Chip designers must resolve in the future is the fact that transistors for digital and memory circuits will be more and more leaky as technology generations advance. Approaches to solving this serious problem will be described. Beyond the quest for low-power solutions lies a promising world of ubiquitous VLSI devices and products ranging from "wireless sensors and tags for everything" to "everything-you-must-do mobile terminals".

### 1.3 Interfacing Electronic Systems to the External World: The New Challenge!

11:05 AM

**Bruno Murari**

STMicroelectronics, Cornaredo, Italy

The dramatic evolution of semiconductor technology over the last 50 years has a real industrial and social revolution that is still ongoing today. The started progress from single-transistor to ULSI circuits has been very fast. As technology proceeded according to the well-known Moore's Law, circuit-design techniques moved more and more from analog to digital following the continuous progress made in microlithography.

While there has been a corresponding huge increase in the computing power of digital circuits, this has not been accompanied by a comparable evolution in the capability of integrated circuits to interface to the external world. For free-standing computers, speed is the key factor. In other applications such as mobile phones, the interfaces with the external world are fundamental and provide the driving force in the evolution of these products. Technologies like BiCMOS, HVCMOS and BCD, which are already available and will further evolve in the future, appear to be more suitable than pure CMOS in satisfying those needs. We are moving now to SoC (System on Chip) and in the future to SiP (System in Package) techniques that will include also micromachined and, even, photonic technologies.

In this paper, both recent and future developments in analog interfaces will be analyzed, with particular attention given to the problem of power-consumption reduction in portable devices. As well, an overview of new applications of MEMS and photonic devices will be presented.

### SESSION 2 SALON 1-6

### **MULTIMEDIA SIGNAL PROCESSING**

Chair: Albert Van der Werf, Philips Research

Laboratories, Eindhoven, The Netherlands

Associate Chair: Hideto Hidaka, Mitsubishi Electric

Hyogo, Japan

# 2.1 A Fully-Integrated 0.13μm CMOS Mixed-Signal SoC for DVD Player Applications

1:30 PM

K. Okamoto, T. Morie, A. Yamamoto, K. Nagano, K. Sushihara, H. Nakahira, R. Horibe, K. Aida, T. Takahashi, M. Ochiai, A. Soneda, T. Kakiage, T. Iwasaki, H. Taniuchi, T. Shibata, T. Ochi, M. Takiguchi,

T. Yamamoto, T. Seike, A. Matsuzawa

Matsushita Electric Industrial, Moriguchi, Japan

A mixed-signal SoC for DVD applications is designed in  $0.13\mu m$  1P 6M CMOS. One DSP, two 32b RISC CPUs, three dedicated processing units, PRML read channel with an analog front end (AFE) and several other subsystems are integrated on the same die. The AFE contains a 5th-order G<sub>m</sub>-C filter and over 66dB C/N. The SoC contains 24M transistors in a 64mm² die and consumes 1.5W at 40MS/s which corresponds to 1.5x DVD playback.

### 2.2 A Single-Chip MPEG2 CODEC for DVD+RW

2:00 PM

J. Geerlings<sup>1</sup>, E. Desmicht<sup>2</sup>, H. de Perthuis<sup>2</sup>

<sup>1</sup>Philips Semiconductors, Eindhoven, The Netherlands

<sup>2</sup>Philips Semiconductors, Caen, France

A single-chip MPEG2 audio/video encoder and decoder is designed for consumer digital recording systems. The chip includes a CPU core with peripherals, a PCI/XIO bus interface, data streaming units to data sources and sinks, graphics engines, video display units and video DACs. The chip contains 32M transistors in  $102 \text{mm}^2$  and is fabricated in a  $0.18 \mu \text{m}$  6M CMOS process.

# 2.3 A 160mW, 80nA Standby, MPEG-4 Audiovisual LSI with 16Mb Embedded DRAM and a 5GOPS Adaptive Post Filter

2:30 PM

H. Arakida¹, M. Takahashi¹, Y. Tsuboi¹, T. Nishikawa¹, H. Yamamoto¹, T. Fujiyoshi¹, Y. Kitasho¹, Y. Ueda¹, M. Watanabe¹, T. Fujita¹, T. Terazawa², K. Ohmori², M. Koana², H. Nakamura³, E. Watanabe¹,

H. Ando<sup>1</sup>, T. Aikawa<sup>1</sup>, T. Furuyama<sup>1</sup>

<sup>1</sup>Toshiba, Kawasaki, Japan

<sup>2</sup>Toshiba Microelectronics, Kawasaki, Japan

<sup>3</sup>Toshiba Information Systems, Kawasaki, Japan

A single-chip MPEG4 audiovisual LSI in a 0.13μm 5M CMOS technology with 16Mb embedded DRAM is presented. Four 16b RISC processors and dedicated hardware accelerators including a 5GOPS post filtering engine are integrated on the IC. The chip consumes 160mW at 125MHz and uses 80nA in the standby mode. This LSI handles MPEG4 CIF video encoding at 15frames/s and audio encoding simultaneously.

BREAK 3:00 PM

### Monday, February 10th 1:30 PM

# 2.4 A 210mW Graphics LSI Implementing Full 3D Pipeline with 264Mtexels/s Texturing for Mobile Multimedia Applications

3:15 PM

R. Woo¹, S. Choi¹, J-H. Sohn¹, S-J. Song¹, Y-D. Bae¹, C-W. Yoon¹, B-G. Nam¹, J-H. Woo¹, S-E. Kim¹, I-C. Park¹, S. Shin², K-D. Yoo², J-Y. Jung², H-J. Yoo¹

<sup>1</sup>KAIST, Daejeon, Republic of Korea

<sup>2</sup>Hynix Semiconductor, Icheon, Republic of Korea

A 121mm² graphics LSI is for portable 2D/3D graphics and MPEG4 applications. The LSI contains a RISC processor with MAC, a 3D rendering engine, 29Mb DRAM and is built in a 0.16µm pure DRAM technology. Programmable clocking allows the LSI to operate in several power modes for various applications. In lower cost mode, power consumption is under 210mW, delivering 264M texture mapped pixels per second.

### 2.5 Image Processor Capable of Block-Noise-Free JPEG2000 Compression with 30frames/s for Digital Camera Applications

3:45 PM

H. Yamauchi, S. Okada, K. Taketa, T. Ohyama, Y. Matsuda, T. Watanabe, S. Okada, T. Mori, Y. Matsuo, Y. Yamada, T. Ichikawa, Y. Matsushita, A. Kobayashi

Sanyo Electric, Gifu, Japan

A one-chip image processor for next-generation digital cameras and broadband PDAs multimedia mobile phones is described. It is capable of processing JPEG2000 data with 30frames/s and a 27MHz operating frequency. The process is fabricated in 0.25 $\mu$ m CMOS and contains 8.5M transistors in a 103mm² area.

### 2.6 A 51.2GOPS Scalable Video Recognition Processor for Intelligent Cruise Control Based on a Linear Array of 128 4-Way VLIW Processing Elements

4:15 PM

S. Kyo, T. Koga, S. Okazaki, R. Uchida, S. Yoshimoto, I. Kuroda NEC, Kawasaki, Japan

A 51.2GOPS fully programmable and scalable video recognition processor is based on a linear connection of 128 4-way VLIW processing elements and an asynchronous data mapping mechanism. Execution is under 33ms/frame for complex weather robust road area/lane marking vehicle detection. The chip contains 21.4M transistors in 121mm² area fabricated in  $0.18\mu m$  7M CMOS.

### 2.7 A 1GOPS Reconfigurable Signal Processing IC with Embedded FPGA and 3-Port 1.2GB/s Flash Memory Subsystem

4:45 PM

M. Borgatti, L. Calì, G. De Sandre, B. Forêt, D. Iezzi, F. Lertora, G. Muzzi, M. Pasotti, M. Poles, P. Rolandi

STMicroelectronics, Agrate Brianza, Italy

A 1GOPS dynamically reconfigurable processing unit with embedded flash memory and SRAM-based FPGA for image/voice processing/recognition applications is described. Code, data and FPGA bitstreams are stored in the embedded flash memory and are independently accessible through 3 content-specific, 64b I/O ports with a peak read rate of 1.2GB/s. The system is implemented in a 0.18μm 2P 6M CMOS flash technology with a chip area of 70mm².

CONCLUSION 5:15 PM

### SESSION 3 SALON 7

### **OVERSAMPLED A/D CONVERTERS**

Chair: Brian Brandt, Maxim Integrated Products,

North Chelmsford, MA

Associate Chair: David Johns, University of Toronto,

Toronto, Canada

# 3.1 A 1.5V 1mA 72dB Passive ΣΔ ADC for a GSM Transceiver in 0.13μm Digital CMOS

1:30 PM

F. Chen, S. Ramaswamy, B. Bakkaloglu Texas Instruments, Dallas, Texas

A passive switched-capacitor  $\Sigma\Delta$  ADC consisting of only switches, capacitors and a comparator, is implemented in a 0.13 $\mu$ m digital CMOS process. This high-speed low-voltage architecture is used in a zero-IF GSM transceiver and has a measured peak SNDR of 67dB over a bandwidth of 100kHz with a SFDR of 75dB and a dynamic range of 72dB. The ADC consumes 1mA from a 1.5V power supply at a clock rate of 104MHz.

### 3.2 A 114dB 68mW Chopper-Stabilized Stereo Multi-Bit Audio A/D Converter

2:00 PM

Y. Yang¹, A. Chokhawala¹, M. Alexander², J. Melanson¹, D. Hester¹¹Cirrus Logic, Austin, TX

<sup>2</sup>Design Consultant, Austin, TX

A fifth-order single-loop seventeen level  $\Sigma\Delta$  modulator with an input feed-forward gain stage and second-order mismatch shaping logic achieves 114dB dynamic range and -105dB THD over the 20kHz audio band. This stereo ADC occupies 5.62mm² active area in a 0.35 $\mu$ m 2P 3M CMOS process and dissipates only 55mW power in the analog circuits.

### 3.3 A 1.2V Dual-Mode WCDMA/GPRS ΣΔ Modulator

2:30 PM

A. Dezzani, E. Andre STMicroelectronics, Crolles, France

A dual-mode  $\Sigma\Delta$  modulator is designed to meet the specifications of a WCDMA/GPRS receiver and is composed of a single-bit second-order modulator followed by a multi-bit stage that adapts performance to broadband signals. The modulator achieves 82dB and 70dB of dynamic range over bandwidths of 100kHz and 1.92MHz, respectively, and dissipates 4.3mW from a 1.2V supply. The circuit is implemented in 0.13 $\mu$ m CMOS technology and occupies an active area of 0.2mm².

BREAK 3:00 PM

### Monday, February 10th 1:30 PM

# 3.4 A Tri-Mode Continuous-Time Σ∆ Modulator with Switched-Capacitor Feedback DAC for a GSM-EDGE/CDMA2000/UMTS Receiver

3:15 PM

R. van Veldhoven

Philips Research, Eindhoven, The Netherlands

Complex continuous-time fifth-order  $\Sigma\Delta$  modulator with 1b quantizer and switched-capacitor feedback DAC for a GSM/CDMA2000/UMTS receiver achieves a dynamic range of 92/83/74dB in 200/1228/3840kHz. Power consumption of one modulator is 3.8/4.1/4.5mW at 1.8V. Processed in 0.18 $\mu$ m CMOS, the 0.55mm² IC includes a PLL, two oscillators and a bandgap reference.

# 3.5 A Continuous-Time Σ∆ Modulator with 88dB Dynamic Range and 1.1MHz Signal Bandwidth

3:45 PM

S. Yan¹, E. Sánchez-Sinencio²

<sup>1</sup>University of Texas, Austin, TX

<sup>2</sup>Texas A&M University, College Station, TX

A baseband continuous-time multi-bit  $\Sigma\Delta$  modulator achieves 88dB dynamic range over a 1.1MHz signal bandwidth consuming 62mW from a 3.3V supply. Excess loop delay encountered in conventional continuous-time modulators is eliminated by the proposed architecture. Clock-jitter sensitivity is considerably reduced compared with prior designs.

### 3.6 A 4.4mW 76dB Complex ΣΔ ADC for Bluetooth Receivers 4:15 PM

K. Philips

Philips Research, Eindhoven, The Netherlands

A  $\Sigma\Delta$  ADC with a fifth-order continuous-time complex loop filter achieves 76dB of DNR in a 1MHz channel. The input impedance is less than  $400\Omega$  and allows operation with a current-mode RF front-end. Image rejection is over 50dB, and IM3 distortion is below -82dBc. The circuit dissipates 4.4mW and is implemented in 0.18 $\mu$ m CMOS.

# 3.7 A Dual Channel $\Sigma\Delta$ ADC with 40MHz Aggregate Signal Bandwidth

4:45 PM

A. Tabatabaei, K. Onodera, M. Zargari, H. Samavati, D. Su Atheros Communications, Sunnyvale, CA

A dual-channel  $\Sigma\Delta$  ADC has been integrated in 0.13 $\mu$ m CMOS technology with an oversampling ratio of 4. The ADC employs a cascade of low-pass and band-pass modulators and achieves an aggregate quadrature signal bandwidth of 40MHz at a sampling frequency of 160MS/s and 54dB dynamic range while dissipating 175mW from a 2.5V supply.

CONCLUSION 5:15 PM

### **SESSION 4 SALON 8**

### **CLOCK RECOVERY AND BACKPLANE TRANSCEIVERS**

Chair: Larry DeVito, Analog Devices, Wilmington, MA

Associate Chair: Stefanos Sidiropoulos, Aeluros,

Mountain View, CA

### 4.1 A 10Gb/s/ch, 50mW 120×130μm² Clock and Data Recovery Circuit

1:30 PM

S. Kaeriyama, M. Mizuno NEC, Sagamihara, Japan

A 10Gb/s clock and data recovery circuit for SerDes macro uses half the power and a quarter the die size of prior art. In 0.15µm CMOS the CDR dissipates 50mW in an area of  $120 \times 130 \mu m^2$  while maintaining a 10Gb/s bandwidth per channel. Jitter tolerance is also improved and the influence of PVT variations is reduced.

### 4.2 A CMOS Multi-Channel 10Gb/s Transceiver

2:00 PM

H. Takauchi¹, H. Tamura¹, S. Matsubara², M. Kibune¹, Y. Doi¹, T. Chiba³, H. Anbutsu¹, H. Yamaguchi¹, T. Mori¹, M. Takatsu¹, K. Gotoh¹, T. Sakai⁴, T. Yamamura⁴

<sup>1</sup>Fujitsu Laboratories, Kawasaki, Japan

<sup>2</sup>Fujitsu LSI Solutions, Kawasaki, Japan

<sup>3</sup>Fujitsu Higashi-Nihon Digital Technology, Sapporo, Japan

⁴Fujitsu, Akiruno, Japan

A quad 10Gb/s transceiver in 0.11 $\mu$ m CMOS communicates electric signals over balanced copper media. The transceiver uses a single 1.2V power supply and dissipates 415mW per channel. One PLL supplies a reference clock to two transmitter channels and two receiver channels. The transceiver contains analog front ends, clock recovery units, and 312MHz parallel interfaces.

### 4.3 A Second-Order Semi-Digital Clock Recovery Circuit Based on Injection Locking

2:30 PM

M-J. Lee', W. Dally², J. Poulton', T. Greer', J. Edmondson', R. Farjad-Rad', H-T. Ng¹, R. Rathi', R. Senthinathan'

<sup>1</sup>Velio Communications, Milpitas, CA

<sup>2</sup>Stanford University, Stanford, CA

A 3.125Gb/s clock recovery circuit in 0.18µm CMOS comprises a multiplying delay-locked loop (MDLL), an injection-locked slave oscillator and a phase control unit. Injection locking reduces MDLL clock distortion and varies the delay of the recovered clock, while a frequency loop in the phase control unit ameliorates the trade off between phase wander and frequency tolerance. Experimental results show high frequency jitter tolerance is improved by 0.08UI.

BREAK 3:00 PM

### Monday, February 10<sup>th</sup> 1:30 PM

#### 4.4 A 2.5 - 10Gb/s CMOS Transceiver with Alternating Edge Sampling Phase Detection for Loop Characteristic Stabilization

3:15 PM

B-J. Lee<sup>1</sup>, M-S. Hwang<sup>1</sup>, S-H. Lee<sup>2</sup>, D-K. Jeong<sup>1</sup> <sup>1</sup>Seoul National University, Seoul, Republic of Korea <sup>2</sup>Silicon Image, Sunnyvale, CA

A 2.5 to 10Gb/s CMOS transceiver in 0.18µm CMOS dissipates 540mW from a 1.8V supply with a BER better than 10<sup>-12</sup>. CDR loop characteristics are stabilized across various jitter environments with small hardware overhead using an alternating edge sampling phase detector.

#### 4.5 8Gb/s Differential Simultaneous Bidirectional Link With 4mV 9ps Waveform Capture Diagnostic Capability

3:45 PM

B. Casper, A. Martin, J. Jaussi, J. Kennedy, R. Mooney Intel Labs, Circuit Research, Hillsboro, OR

Differential simultaneous bidirectional I/O circuits in 0.18µm CMOS operate up to 8Gb/s with BER better than 10<sup>-11</sup> using 32b LFSR. The cell area is 0.13mm<sup>2</sup> and the dissipation is 120mW. On-die diagnostic measurement of individual I/O link performance is enabled with a variable offset comparator and clock phase interpolator with resolution of 4mV and 9ps.

#### 4.6 Equalization and Clock Recovery for a 2.5 - 10Gb/s 2-PAM/4-PAM Backplane Transceiver Cell

4:15 PM

J. Zerbe<sup>1</sup>, C. Werner<sup>1</sup>, V. Stojanovic<sup>1</sup>, F. Chen<sup>1</sup>, J. Wei<sup>1</sup>, G. Tsang<sup>1</sup>, D. Kim<sup>1</sup>, W. Stonecypher<sup>1</sup>, A. Ho<sup>1</sup>, T. Thrush<sup>1</sup>, R. Kollipara<sup>1</sup>, G-J. Yeh<sup>1</sup>, M. Horowitz<sup>2</sup>, K. Donnelly<sup>1</sup> <sup>1</sup>Rambus, Los Altos, CA

<sup>2</sup>Stanford University, Stanford, CA

A backplane transceiver uses a folded 5-tap TX equalizer and 5-tap RX equalizer to counteract losses and reflections. A flexible 2-PAM/4-PAM CDR uses select transitions for receive clock recovery. BER better than 10<sup>-15</sup> at 10Gb/s and power <60mW/Gb are measured values for a 16" backplane with two high speed connectors.

#### 4.7 A 2.7Gb/s CDMA-Interconnect Transceiver Chip Set with Multi-Level Signal Data Recovery for Re-Configurable **VLSI Systems**

4:45 PM

Z. Xu<sup>1</sup>, H. Shin<sup>2</sup>, J. Kim<sup>1</sup>, F. Chang<sup>1</sup>, C. Chien<sup>1</sup> <sup>1</sup>University of California, Los Angeles, CA <sup>2</sup>Qualcomm, San Diego, CA

A 2.7Gb/s interconnect transceiver chip-set based on Code Division Multiple Access (CDMA) is described and implemented in 0.18µm CMOS technology to achieve real-time system re-configurability and multiple I/O communication. The transceiver chip-set, with an Alexander-type multilevel data recovery circuit, can reconfigure multiple I/O signal routes within a symbol period of 0.8ns. The chip-set dissipates 74mW and occupies 0.3mm<sup>2</sup> per I/O pair.

CONCLUSION 5:15 PM

### SESSION 5 SALON 9

### **WIRELESS PAN TRANSCEIVERS**

Chair: Thomas Lee, Stanford University, Stanford, CA

Associate Chair: Mary Jo Nettles, Mobilian, San Diego, CA

5.1 A Dual-Mode 802.11b/Bluetooth Radio in 0.35μm CMOS

H. Darabi<sup>1</sup>, J. Chiu<sup>1</sup>, S. Khorram<sup>1</sup>, H. Kim<sup>1</sup>, Z. Zhou<sup>1</sup>, S. Jiang<sup>1</sup>, K. Evans<sup>2</sup>, E. Chien<sup>1</sup>, B. Ibrahim<sup>1</sup>, E. Geronaga<sup>1</sup>, L. Tran<sup>1</sup>, R. Rofougaran<sup>1</sup> Broadcom, El Segundo, CA

<sup>2</sup>SolarFlare Communications, Irvine, CA

A dual-mode CMOS 2.4GHz transceiver consumes 65mA in RX and 78mA in TX from a 3V supply. The receiver achieves a typical sensitivity of -88dBm at 11Mb/s for 802.11b, and -83dBm for Bluetooth mode. The receiver minimum IIP3 is -8dBm, and the transmitter delivers a nominal output power of 0dBm, with a power control range of 20dB in 2dB steps.

### 5.2 A 2.4GHz Dual-Mode 0.18μm CMOS Transceiver for Bluetooth and 802.11b

2:00 PM

T. Cho<sup>1</sup>, D. Kang<sup>1</sup>, S. Dow<sup>2</sup>, C-H. Heng<sup>1</sup>, B. Song<sup>3</sup> Wireless Interface Technologies, San Diego, CA

<sup>2</sup>Santel Networks, Newark, CA

3University of California, San Diego, CA

A 2.4GHz dual-mode RF transceiver IC implements transmit and receive functions for both Bluetooth with -80dB sensitivity and 802.11b Wireless LAN with -88dB sensitivity in a single chip without doubling the required silicon area. Implemented in 0.18μm CMOS process, the circuit operates at 1.8V, and die size is 16mm² including pads.

### 5.3 A 43mW Bluetooth Transceiver with -91dBm Sensitivity 2:30 PM

C. Cojocaru<sup>1</sup>, T. Pamir<sup>1</sup>, F. Balteanu<sup>1</sup>, A. Namdar<sup>1</sup>, D. Payer<sup>2</sup>, I. Gheorghe<sup>1</sup>, T. Lipan<sup>1</sup>, K. Sheikh<sup>1</sup>, J. Pingot<sup>1</sup>, H. Paananen<sup>3</sup>, M. Littow<sup>2</sup>, E. Macrobbie<sup>1</sup>, M. Cloutier<sup>1</sup>

<sup>1</sup>Skyworks Solutions, Ottawa, Ontario, Canada

<sup>2</sup>Conexant Systems, San Diego, CA

<sup>3</sup>Nokia Research Center, Tokyo, Japan

A Bluetooth transceiver has -91dBm sensitivity while drawing 24mA from a 1.8V supply. The receiver has a low-IF path with 30dB image and 9dB co-channel rejection, 80dB of AGC, digital equalization and complex PLL demodulation. The transmitter uses direct two-point modulation and draws 18mA at +6dBm output power. The DS PLL settles in 100 $\mu s$ . LDO regulators power the analog and digital sections.

BREAK 3:00 PM

### Monday, February 10th 1:30 PM

# 5.4 An Experimental Coin-sized Radio for Low Power WPAN (IEEE 802.15.4) Applications at 2.4GHz

3:15 PM

P. Choi, H. Park, I. Nam, K. Kang, Y. Ku, S. Shin, S. Park, T. Kim, B. Kim, H. Choi, S. Kim, S. Park, M. Kim, S. Park, K. Lee KAIST, Daejeon, Republic of Korea

A 2.4GHz radio for IEEE 802.15.4 WPANs using 0.18µm CMOS technology consumes 21mW and 30mW at 1.8V supply in RX and TX mode, respectively. The receiver utilizes a low-IF architecture with a poly-phase filter and transistor linearization technique. A ROM-based DSSS GMSK signal is directly up-converted using I/Q mixing. Silicon area is 8.75mm².

# 5.5 A Single-Chip CMOS Bluetooth Transceiver with 1.5MHz IF and Direct Modulation Transmitter

3:45 PM

H. Ishikuro, M. Hamada, K. Agawa, S. Kousai, H. Kobayashi, D. Nguyen, F. Hatori

Toshiba, Kawasaki, Japan

A single-chip Bluetooth transceiver in 0.18µm CMOS integrates a direct VCO modulation transmitter and 1.5MHz-IF receiver to reduce power consumption and cost. The receiver achieves a sensitivity of -77dBm and transmitting power of +4dBm.

### 5.6 A Low Power CMOS Bluetooth Transceiver with a Digital Offset Canceling DLL-Based GFSK Demodulator

4:15 PM

C-H. Park<sup>1</sup>, S. Byun<sup>2</sup>, Y. Song<sup>2</sup>, S. Wang<sup>2</sup>, C. Conroy<sup>3</sup>, B. Kim<sup>3</sup> <sup>1</sup>Stelsys Telecom, Seoul, Republic of Korea <sup>2</sup>KAIST, Daejeon, Republic of Korea <sup>3</sup>Berkana Wireless, San Jose, CA

A 0.18µm CMOS Bluetooth IC consumes 33mA in RX mode and 25mA in TX mode. The IC has a DLL-based GFSK demodulator with frequency offset cancellation. The receiver has -78dBm sensitivity at 0.1% BER, and the transmitter delivers a nominal 0dBm power level with 20dB control.

### 5.7 CMOS Differential LC Oscillator with Suppressed Up-Converted Flicker Noise

4:45 PM

A. Ismail, A. Abidi University of California, Los Angeles, CA

A 1.5GHz CMOS differential VCO reduces the spectral density of up-converted flicker noise by 20dB, thereby reaching the phase noise target of -105dBc/Hz at 50kHz offset required for the PDC receive VCO. Flicker noise is suppressed by this amount across almost the entire tuning range from 1.43 to 1.64GHz, while drawing 6mA from a 2.7V supply.

CONCLUSION 5:00 PM

### SESSION 6 SALON 10-15

### LOW-POWER DIGITAL TECHNIQUES

Chair: Ron Preston, Intel, Shrewsbury, MA

Associate Chair: Masayuki Mizuno, NEC, Sagamihara-shi,

Kanagawa, Japan

6.1 Dynamic-Sleep Transistor and Body Bias for Active Leakage Power Control of Microprocessors

1:30 PM

J. Tschanz, S. Narendra, Y. Ye, B. Bloechel, S. Borkar, V. De Intel, Hillsboro, OR

Sleep transistors and body bias are used to control active leakage for a 32b integer execution core implemented in a 100nm dual  $V_{\scriptscriptstyle T}$  CMOS technology. A PMOS sleep transistor degrades performance by 4% but offers 20X leakage reduction which is further improved with body bias. Time constants for leakage convergence range from 30ns to 300ns allowing 9-44% power savings for idle periods greater than 100 clock cycles.

### 6.2 A Shared-Well Dual-Supply-Voltage 64-bit ALU

2:00 PM

Y. Shimazaki<sup>1</sup>, R. Zlatanovici<sup>2</sup>, B. Nikolic<sup>2</sup>

<sup>1</sup>Hitachi, Tokyo, Japan

<sup>2</sup>University of California, Berkeley, CA

A shared N-well, dual-supply-voltage 64b ALU module in 0.18μm, 1.8V CMOS 1P 5M technology operates at 1.16GHz on a 9mm² die. For a target delay increase of 2.8%, energy savings are 25.3% using dual supplies. An 8.3% increase in delay, saves 33.3% in energy.

# 6.3 0.5V, 400 MHz, $V_{DD}$ -Hopping Processor with Zero $V_{TH}$ FD-SOI Technology

2:30 PM

H. Kawaguchi¹, T. Miyazaki², D. Yamada², D. Antono², S. Hattori³, K. Kanda², K. Nose⁴, K. Inagaki², T. Hiramoto², T. Sakurai²

<sup>1</sup>University of Tokyo, Tokyo, Japan

<sup>2</sup>University of Tokyo, Tokyo, Japan

3KDDI, Tokyo, Japan

<sup>4</sup>NEC, Tokyo, Japan

A 0.5V, 400MHz, 3.5mW, 16b RISC processor with a 0.25 $\mu$ m, dual V<sub>TH</sub>, fully-depleted SOI technology is presented. Zero V<sub>TH</sub> is used in logic for high speed while memories and register files adopt a higher V<sub>DD</sub> and V<sub>TH</sub> to suppress leakage. Experimental results show that V<sub>DD</sub>-hopping is effective in leakage dominant environments.

BREAK 3:00 PM

### 6.4 An Autonomous Decentralized Low-Power System with Adaptive-Universal Control for a Chip Multi-Processor

3:15 PM

M. Miyazaki, G. Ono, H. Tanaka, N. Ohkubo, T. Kawahara Hitachi, Central Research Laboratory, Tokyo, Japan

A technique for adaptive-universal control of clock frequency, supply voltage, and body bias optimizes the performance-to-power ratio of chip multiprocessors. The technique is based on a compound built-in self-test and self-instructed look-up table scheme for an autonomous and decentralized system. Applied to a 32b ALU, power is reduced by seventy times.

### Monday, February 10th 1:30 PM

### 6.5 A 400MHz 183mW Microcontroller in Body-Tied SOI Technology

3:45 PM

H. Sato, N. Itoh, K. Yoshida, Y. Nakase, H. Makino, A. Yamada, T. Arakawa, S. Iwade, T. Ipposhi Mitsubishi Electric, Hyogo, Japan

A low-power microcontroller is designed in  $0.10\mu m$  body-tied SOI CMOS technology by reusing existing design resources developed in  $0.18\mu m$  bulk CMOS. Only two new masks are needed for this work. The performance is evaluated by simulations and indicates operation at 400MHz with 183mW dissipation at 0.8V and represents a five-times improvement in power-delay product.

### 6.6 A 3.5GHz 32mW 150nm Multiphase Clock Generator for High-performance Microprocessors

4:15 PM

A. Alvandpour¹, R. Krishnamurthy¹, D. Eckerbert², S. Apperson¹, B. Bloechel¹, S. Borkar¹

<sup>1</sup>Intel. Hillsboro. OR

<sup>2</sup>Chalmers University, Goteborg, Sweden

A 3.5GHz 8-phase all-digital clock generator is fabricated in 150nm CMOS to achieve scalable 1.7x frequency-range and 9ps end-to-end time resolution measured at 1.6V, 110°C. A closed-to-open loop control scheme enables 32mW open-loop power consumption, 300µW at clock gate-off, zero-cycle response during clock re-enable, and <4% static phase error.

### 6.7 A 0.3V 3.6GHz 0.3mW Frequency Divider with Differential ED-CMOS/SOI Circuit Technology

4:45 PM

T. Douseki<sup>1</sup>, T. Shimamura<sup>1</sup>, N. Shibata<sup>2</sup> NTT, Atsugi, Japan <sup>2</sup>NTT Electronics, Tokyo, Japan

A differential ED-CMOS/SOI circuit combines both zero  $V_{\text{T}}$  CMOS/SOI and ED-MOS/SOI circuits and operates at supply voltages as low as 0.3V. An experimental frequency divider, fabricated in a 0.25 $\mu$ m fully-depleted SOI process, achieves a maximum operating frequency of 3.6GHz at 0.3V and 5.4GHz at 0.5V while reducing power dissipation to less than 1mW.

# 6.8 A 9μW 50MHz 32b Adder Using a Self-Adjusted Forward Body Bias in SoCs

5:00 PM

K. Ishibashi, T. Yamashita, Y. Arima, I. Minematsu, T. Fujimoto STARC, Yokohama, Japan

This 32b adder in a  $0.13\mu m$  CMOS process consumes  $9\mu W$  at 50MHz and 0.3V and operates at 500MHz at 0.6V. Forward body biases are self-adjusted to minimize the threshold voltage and reduce PVT dependence. The power of the SoC can be reduced to 1/4 that of standard CMOS by gating the forward body bias in the IP blocks.

**CONCLUSION 5:15 PM**

### **DISCUSSION SESSIONS**

E1: Analog IP — Stairway to SoC Heaven?

(Salon 7)

Organizer: Rudolf J. Koch, Infineon Technologies, Munich, Germany Moderator: Franz Dielacher, Infineon Technologies, Villach, Austria

Exploding costs in ultra-deep-submicron technologies make any redesign extremely expensive. Stringent time-to-market constraints and fast-technology evolutions are putting the analog designers under high pressure. Fast safe design and implementation of analog functions is therefore urgently needed. In the past, analog synthesis has promised these benefits, yet has failed. Is Analog IP to be the next vision doomed to failure? Can new, less-ambitious paradigms finally make analog Electronic Design Automation (EDA) for SoC a success story? Or, will SoC prove to be a short-lived vision?

#### Panelists:

Yousif Ammar, CEO, XIGNAL, Unterhaching, Germany Georges Gielen, Professor, Katholieke Universiteit Leuven, Leuven, Belgium

Thomas Heydler, President/CEO, Barcelona Design, Newark, CA Masao Hotta, Senior Chief Engineer & General Manager, Hitachi. Gunma-ken. Japan

Philippe Magarshack, Vice-President, STMicroelectronics Central R&D Group, Crolles, France

Jean-Francois Pollet, COO, Dolphin Integration, Meylan, France Bill Redman-White, Fellow, Philips, Semiconductor / Professor, Southampton University, United Kingdom

# E2: Will MEMS, Imagers, and Displays Be Key to the Growth of the IC Industry?

(Salon 8)

Organizer: Khalil Najafi, Professor, Department of Electrical

Engineering and Computer Science, University of

Michigan, Ann Arbor, MI

Moderator: Kensall D. Wise, Professor, Department of Electrical

Engineering and Computer Science, University of

Michigan, Ann Arbor, MI

This panel will discuss how the IC industry can tap into new markets driven by imagers/displays/MEMS. The panelists will tackle several questions: Will the IC industry continue to grow based only on faster/bigger digital/analog chips? Will computing and communications be the biggest growth markets for ICs, or will imagers/displays/MEMS needed in toys, healthcare, environmental sensing, etc. help expand the applications of ICs? Will there be more MEMS on IC chips? Will conventional ICs become only a small part of microsystems as MEMS/imagers/displays take away a bigger piece of the system's pie?

### Panelists:

Yoshiaki Hagiwara, Principal Engineer, Sony, Tokyo, Japan Christofer Hierold, Professsor, Swiss Federal Institute of Technology, Zurich, Switzerland

Roger Howe, Professor, Department of Electrical Engineering and Computer Science, University of California, Berkeley, CA

R. Daniel McGrath, Andover, MA

Clark C.T. Nguyen, Program Manager, Microsystems Technology Office, DARPA

Ray Roop, Director, Strategic Technology, Sensor Products Division, Motorola, Tempe, AZ

### Monday, February 10th 8:00 PM

E3: Good, Bad, Ugly — 50 Years of Memory Evolution. What Next?

(Salon 9)

Organizer: John Barth, Senior Engineer, IBM Microelectronics,

Burlington, VT

Moderator: Sreedhar Natarajan, Design Manager, Mosys,

Kanata, Canada

In light of the up-coming 50th anniversary of the ISSCC, the memory subcommittee has chosen to review memory evolution over the past 50 years. This panel will address the surviving innovative memory technologies as well as the failures in memory technology. Many memory technologies have come and gone (CCD, Bubble, etc.). The panelists will isolate the good, bad and the absolutely impractical (or ugly) memory technologies in the last 50 years.

#### Panelists:

Howard Kalter, President, HLK, Burlington, VT

Dick Foss, Chairman, Mosaid Technologies, Calabogie, Canada

Adin Hyslop, Director of Design, Ramtron International,

Colorado Springs, CO

Changhyun Kim, Vice President, Memory Division, Samsung, Hwasung, Republic of Korea

Joel Karp, Consultant, Atherton, CA

Roelof Salters, Research Fellow, Philips Semiconductors,

Eindhoven, The Netherlands

### SESSION 7 SALON 1-6

#### DACS AND AMPS

Chair: Ken Poulton, Agilent Laboratories, Palo Alto, CA

Associate Chair: Roy Scott Kaller, Standard Microsystems,

Phoenix, AZ

# 7.1 A 16b 400MS/s DAC with -80dBc IMD to 300MHz and -160dBm/Hz Noise Power Spectral Density

8:30 AM

W. Schofield, D. Mercer, L. St. Onge Analog Devices, Wilmington, MA

A current-output DAC with on-board calibration engine guarantees 16b monotonicity and achieves better than -160dBm/Hz noise power spectral density. Well bootstrapping, local bias generation and constant data activity techniques are combined to achieve better than -80dBc IMD to 300MHz at 400MS/s.

### 7.2 A 1.5V 14b 100MS/s Self-Calibrated DAC

9:00 AM

Y. Cong, R. Geiger Iowa State University, Ames, IA

A calibrated 14b current-steering DAC is fabricated in a 0.13µm digital CMOS process. The DAC achieves 14b static linearity with a single 1.5V supply, and the core occupies 0.1mm². Dynamic linearity is improved through reduction of parasitic effects. At 100MS/s, the SFDR is 82dB and 62dB at signals of 0.9MHz and 42.5MHz, respectively. Power consumption is 16.7mW.

### 7.3 A 4 x 40W Digital Input Class-AB Power DAC with 100dB Dynamic Range

9:30 AM

C. Meroni<sup>1</sup>, E. Botti<sup>1</sup>, A. Grosso<sup>1</sup>, F. Stefani<sup>1</sup>, M. Ghioni<sup>2</sup>, A. Baschirotto<sup>3</sup> <sup>1</sup>STMicroelectronics, Milan, Italy

<sup>2</sup>Politecnico di Milano, Milan, Italy

<sup>3</sup>Universitá di Lecce, Lecce, Italy

A 4 x 40W power DAC for car-radio audio systems has a 100dB dynamic range and is realized in a 0.6 $\mu$ m BiCMOS/DMOS technology. EMI is reduced using a multi-bit DAC with a current-mode interface, DDWA algorithm and a class-AB amplifier with 2nd-order filtering. Total output noise of 25 $\mu$ V $_{\text{RMS}}$  without signal yields a 110dB SNR.

**BREAK 10:00 AM**

### 7.4 A 500MHz CMOS Anti-Alias Filter using Feedforward Opamps with Local Common-Mode Feedback

10:15 AM

J. Harrison, N. Weste Macquarie University, Marsfield, Australia

A 500MHz op-amp-RC filter in a 0.18 $\mu$ m CMOS process achieves an integrator signal swing of  $1.73V_{\mbox{\tiny pp}}$  for -40dB THD and thermal noise of 18nV/ $\sqrt{\mbox{Hz}}$ . A three-stage op-amp with two feed-forward paths and common-mode feedback local to each stage is used. The op-amp features 8GHz unity-gain frequency and 40dB gain at 500MHz.

### Tuesday, February 11th 8:30 AM

### 7.5 A Class-D Output Stage with Zero Dead Time

10:45 AM

M. Berkhout

Philips Semiconductors, Nijmegen, The Netherlands

An integrated class-D output stage has been realized with zero dead time, thereby removing one of the dominant sources of distortion in class-D amplifiers. Dead time is eliminated through proper dimensioning of the power transistor drivers and accurate matching of switch timing. Open-loop distortion of this output stage stays below 0.1% up to 35W.

### 7.6 A Baseband Gain-Controlled Amplifier with a Linear-in-dB Gain Range from 14dB to 76dB and a Fixed Corner Frequency DC Offset Canceler

11:15 AM

T. Arai1, T. Itakura2

<sup>1</sup>Toshiba Semiconductor, Kawasaki, Japan

<sup>2</sup>Toshiba R&D Center, Kawasaki, Japan

A linear-in-dB gain-control amplifier for direct conversion systems employs linearized transconductors in a core amp, a dc offset canceller, and a gain control circuit. The offset compensation circuit achieves a constant corner frequency over a gain range of 14 to 76dB by simultaneous tuning of the transconductors.

### 7.7 A 3A 20MHz BiCMOS/DMOS Power Operational Amplifier: A Structural Design Approach

11:45 AM

V. Ivanov, D. Baum Texas Instruments, Tucson, AZ

Design of a power op-amp using a structural design methodology is presented. The BiCMOS/DMOS op-amp features rail-to-rail output, 3A maximum output current, adjustable current limit without delay, a class AB input stage with a 50V/ $\mu$ s slew rate, and 100dB open-loop gain with a 2 $\Omega$  load. It consumes 50mA from a single 7-16V supply.

**CONCLUSION 12:15 PM**

### **SESSION 8 SALON 7**

#### COMMUNICATION SIGNAL PROCESSING

Chair: Bernard Shung, Broadcom, San Jose, CA

Associate Chair: Thucydides Xanthopoulos, Cavium Networks,

Marlborough, MA

### 8.1 A High Performance SSL, IPSEC Protocol Aware Security Processor

8:30 AM

D. Carlson, D. Brasili, A. Hughes, A. Jain, T. Kiszely, P. Kodandapani, A. Vardharajan, T. Xanthopoulos, V. Yalala Cavium Networks, Santa Clara, CA

A 64M transistor security macro processor enabling 40k full SSL handshakes per second with 1024b RSA. The 3DES, AES, ARC4, SHA-1, MD5 and modular exponentiation cryptographic primitives are also supported. The processor is fabricated in a 0.13 $\mu$ m 8M CMOS process and consumes 12W at 500MHz.

# 8.2 A Single-Chip 802.11a MAC/PHY with a 32b RISC Processor

9:00 AM

T. Fujisawa<sup>1</sup>, J. Hasegawa<sup>1</sup>, K. Tsuchie<sup>1</sup>, T. Shiozawa<sup>1</sup>, T. Fujita<sup>1</sup>, K. Seki-Fukuda<sup>2</sup>, T. Higashi<sup>2</sup>, R. Bandai<sup>2</sup>, N. Yoshida<sup>3</sup>, K. Shinohara<sup>3</sup>, T. Watanabe<sup>3</sup>, H. Hatano<sup>3</sup>, K. Noguchi<sup>3</sup>, T. Saito<sup>1</sup>, Y. Unekawa<sup>1</sup>, T. Aikawa<sup>1</sup> Toshiba Semiconductor, Kawasaki, Japan

<sup>2</sup>Toshiba Microelectronics, Kawasaki, Japan

<sup>3</sup>Toshiba Information System, Kawasaki, Japan

An 802.11a compliant MAC/PHY processing chip has been successfully fabricated in  $0.18\mu m$  CMOS. Thirty million transistors are integrated on a  $10.91 \times 10.91 mm^2$  die in a 361-pin PFBGA. The MAC functions are fully implemented by firmware on an embedded 32b RISC processor and hardware acceleration logic. The PHY supports a complete set of data rates up to 54 Mb/s.

## 8.3 Dual Antenna UMTS Mobile Station Transceiver ASIC for 2Mb/s Data Rate

0-30 VM

A. Eltawil<sup>1</sup>, E. Grayver<sup>1</sup>, H. Zou<sup>1</sup>, J. Frigon<sup>1</sup>, G. Poberezhskiy<sup>1</sup>, B. Daneshrad<sup>2</sup>

<sup>1</sup>Innovics Wireless, Los Angeles, CA

<sup>2</sup>University of California, Los Angeles, CA