# ADVANCE PROGRAM

# IEEE INTERNATIONAL SOLID-STATE **CIRCUITS** CONFERENCE

**FEBRUARY** 6, 7, 8, 9, 10

# CONFERENCE THEME:

**Entering the Nanoelectronic Integrated-Circuit Era**

> SAN FRANCISCO MARRIOTT HOTEL

SUNDAY ALL-DAY: 2 FORUMS: High-Frequency Clock Generation; Advanced DRAM; 8TUTORIALS 3 SPECIAL-TOPIC SESSIONS: Powerline LAN; Processor Power Problems; 3D Integration ALL-DAY: 3 FORUMS: Imager Characterization; Nanoscale Design; Automotive Circuits; SHORT COURSE: RF Circuits & Systems

The International Solid-State Circuits Conference is the foremost global forum for the presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers, working at the cutting edge of IC design and application, to maintain technical currency and to network with leading experts.

#### CONFERENCE HIGHLIGHTS

On Sunday, February 6, the day before the official opening of the Conference, ISSCC 2005 offers:

- · A choice of up to 3 of a total of 8 Tutorials

- Two ISSCC Advanced Solid-State Circuit Design Forums:

- GIRAFE (GHz Radio Front End) Advanced Solid-State Circuit Design Forum: "Clock and Frequency Generation for Wireless and Wireline Applications"

- Memory Circuit Design Forum: "Advanced Dynamic-Memory Design"

The 90-minute tutorials offer background information and a review of the current state-of-the-art in specific circuit-design topics. In the all-day Advanced Solid-State Circuit Design Forums, leading experts present state-of-the-art design strategies in a workshop-like format. The Forums are targeted at designers experienced in the technical field.

On Sunday evening, three Special-Topic Evening Sessions addressing nextgeneration circuit-design challenges will be offered, starting at 7:30PM:

- Powerline LAN

- When Processors Hit the Power Wall

- 3D System-on-Package

- The Special-Topic Evening Sessions are open to all ISSCC attendees.

On Monday, February 7, a record ISSCC technical program of 233 papers in 6 parallel session, starts with 3 plenary talks: "Nanoelectronics for the Ubiquitous Information Society"; "Ambient Intelligence: Broad Dreams and Nanoscale Realities"; Innovation and Integration in the Nanoelectronics Era". A Social Hour, open to all ISSCC attendees, will follow the afternoon session. The Social Hour will feature posters from the winners of the 2003-04 and 2004-05 joint DAC-ISSCC student-design contest. Monday evening features two panel discussions and a Special-Topic Evening Session: Highlights of the Symposium on VLSI Technology, in which some of ISSCC-relevant papers from the Symposium are presented to intrigue and inspire ISSCC attendees.

On Tuesday, February 8, ISSCC 2005 offers morning and afternoon technical sessions, followed by a Social Hour, a Special-Topic Evening Session on Nanoscale SRAM and two panel discussions. Wednesday, February 9, features morning and afternoon technical sessions.

On Thursday, February 10, ISSCC 2005 offers a choice of four events:

- An ISSCC Short Course: "RF Circuit Design from Technology to Systems". Two sessions of the Short Course will be offered, with staggered starting times.

- An ISSCC Advanced Solid-State-Circuit-Design Forum "Automotive Technology and Circuits".

- An ISSCC Advanced Solid-State-Circuit-Design Forum on Microprocessor Design: "Robust Design Solutions for Nanoscale Circuits: From DFM through End-of-Life".

- An ISSCC Advanced Solid-State-Circuit-Design Forum: "Characterization of Solid-State Image Sensors".

Registration for the Thursday events is limited. Registration will be filled on a first-come first-served basis. Use of the ISSCC Web-registration site (www.isscc.org) is strongly encouraged. Web registrants will be provided with immediate confirmation on registration for Tutorials, Advanced Solid-State-Circuit-Design Forums, and the Short Course.

## **CONTENTS**

| Tutorials    |                                                                          |        |  |  |

|--------------|--------------------------------------------------------------------------|--------|--|--|

| F1           | <b>FORUMS</b> GIRAFE Forum                                               | a      |  |  |

| F2           | Memory Forum                                                             |        |  |  |

| -            | SPECIAL-TOPIC SESSIONS                                                   |        |  |  |

| SE1          | Powerline LAN: Is There a Concrete Wall Dividing Wireless from Wireline? | 3      |  |  |

| SE2          | When Processors Hit the Power Wall (or "When the CPU hits the fan")      |        |  |  |

| SE3          | Integration in the 3rd Dimension:                                        |        |  |  |

|              | Opportunities and Challenges                                             | 5      |  |  |

| 1            | Plenary Session                                                          | 7      |  |  |

| 2            | Non-Volatile Memory                                                      | 9      |  |  |

| 3            | Backplane Transceivers                                                   |        |  |  |

| 4            | TD: Mixed-Domain Systems                                                 |        |  |  |

| 5            | WLAN Transceivers                                                        | 5      |  |  |

| 6            | High-Speed and Oversampled DACs                                          | 7      |  |  |

| 7            | Multimedia Processing                                                    |        |  |  |

|              | DISCUSSION SESSIONS                                                      |        |  |  |

| E1           | Mobile Imaging: Paradigm Shift or Technology Bubble?30                   |        |  |  |

| E2           | What Papers Will and Will Not Be at ISSCC2010?                           | 0      |  |  |

| SE4          | Toward the Nanoscale Transistor - Highlights of 2004                     |        |  |  |

|              | Symposium on VLSI Technology3                                            | 1      |  |  |

|              | PAPER SESSIONS                                                           | _      |  |  |

| 8            | Circuits for High-Speed Links and Clock-Generators                       | 3      |  |  |

| 9            | Switched-Capacitor $\Delta\Sigma$ Modulators                             | 5      |  |  |

| 10           | Microprocessors and Signal Processing                                    |        |  |  |

| 11           | Ultra Wideband Solutions                                                 |        |  |  |

| 12<br>13     | Optical Communications                                                   |        |  |  |

| 14           | TD: Low-Power Wireless and Advanced Integration                          |        |  |  |

| 15           | ADCs, DC References, and Converters                                      |        |  |  |

| 16           | Clock Distribution and Power Control                                     | á      |  |  |

| 17           | RF Cellular ICs                                                          |        |  |  |

|              | ference Timetable                                                        |        |  |  |

| Conf         | ference Registration and Hotel-Reservation FormsInsert                   | s      |  |  |

| 18           | High-Speed Interconnects and Building Blocks                             | 5      |  |  |

| 19           | Imagers                                                                  |        |  |  |

|              | DISCUSSION SESSIONS                                                      |        |  |  |

| SE5          | SRAM Design in the Nanoscale Era                                         | 8      |  |  |

| E3           | RF MEMS: Fact or Stiction59                                              | 9      |  |  |

| E4           | Driving Miss Ubiquity: What applications will fill tomorrow's fabs? 59   | 9      |  |  |

| 00           | PAPER SESSIONS                                                           | _      |  |  |

| 20           | Processor Building Blocks                                                |        |  |  |

| 21           | TD: RF Trends: Above-IC Intergration and MM-Wave62-63                    |        |  |  |

| 22           | PLL, DLL, And VCOs                                                       | 5      |  |  |

| 23<br>24     | Pageband Processing 69.69                                                | /<br>n |  |  |

| 25           | Baseband Processing                                                      | 9      |  |  |

| 26           | Static Memory                                                            |        |  |  |

| 27           | Filters and Continous Time $\Delta\Sigma$ Converters                     |        |  |  |

| 28           | Clocking and I/O                                                         |        |  |  |

| 29           | RF Techniques                                                            |        |  |  |

| 30           | Displays and Biosensors                                                  |        |  |  |

| 31           | Mass Storage                                                             | 2      |  |  |

| 32           | TD: Advanced Array Structures                                            | 3      |  |  |

| Shor         | Short Course: RF Circuit Design from Technology to Systems 84-85 FORUMS  |        |  |  |

| F3           | Characterization of Solid-State Image Sensors                            | 7      |  |  |

| F4           | Robust Design Solutions for Nanoscale Circuits:                          | _      |  |  |

|              | From DFM through End-of-Life                                             |        |  |  |

| F5           | ATAC: Automotive Technology and Circuits                                 |        |  |  |

| Information  |                                                                          |        |  |  |

|              | Committees                                                               |        |  |  |

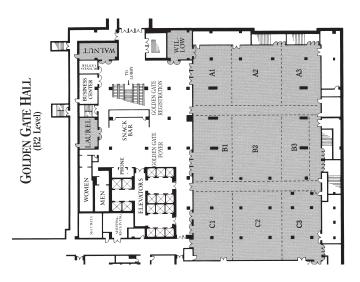

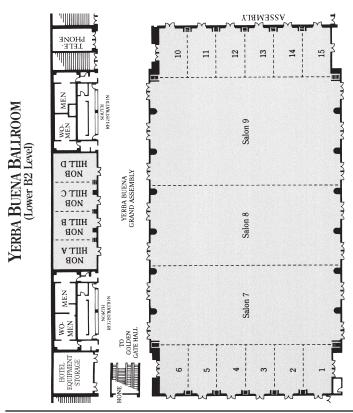

| Hotel Layout |                                                                          |        |  |  |

| OUIII        |                                                                          | _      |  |  |

#### T1: INTEGRATED POWER MANAGEMENT

As circuit-design power requirements never align well with the available power source, power management along with efficiency and cost are critical elements in all system designs. This tutorial provides an overview of dc/dc converter techniques (switched-inductor, switched-capacitor, linearregulator, and compound architectures), and offers a discussion of the pros and cons for each. The characteristics of today's portable power sources, lithium-ion batteries being the most common, are also discussed. Finally, the focus is on circuit techniques which may be integrated into CMOS Systems-on-a-Chip when multiple supply voltages are required.

Instructor: Roy Kaller is Vice President of Engineering at SMSC in Phoenix, AZ where he is responsible for analog technology development and design automation. He joined SMSC as part of the company's acquisition of Gain Technology Corporation in June 2002. Prior to joining Gain Technology in 2000, he was the founder and director of National Semiconductor's Power Management design center in Grass Valley, CA. From 1992 until 1995, Roy was a design engineering manager for Silicon Systems, and he started his career at Burr-Brown Corporation in 1983 where he developed a broad range of products including precision opamps, MUXes, DACs, and ADCs. Roy has been a member of ISSCC Analog Sub-committee since 2002, has published eight papers and holds one patent in analog integrated circuits and solid state chemistry. Roy earned his BSEE from the University of Arizona and is a graduate of the University's Arizona Executive Program.

#### INTRODUCTION TO I/O DESIGN FOR DIGITAL SYSTEMS T2:

This tutorial gives an introduction to digital I/O circuit design. Topics include essential transmission line theory, elements of transmitter and receiver design (boundary-scan blocks, up/down converters, line drivers and receivers, and ESD protection structures). In addition to more advanced topics such as differential I/O structures, on-chip termination, PVT compensation and clocking for I/O interfaces are discussed.

Instructor: Thucydides Xanthopoulos received his BS, MS, and PhD in Electrical Engineering and Computer Science from the Massachusetts Institute of Technology in 1992, 1995, and 1999, respectively. From 1999 to 2001 he was a consulting engineer with the Alpha Development Group, Compaq Computer in Shrewsbury, MA, where he designed the clock-generation and distribution network for the Alpha 21364 server processor (EV7). Since 2001, he has been a principal member of Technical Staff with Cavium Networks in Marlboro, MA, where he co-leads silicon implementation of security and network services processors and is primarily responsible for I/O, clocking, power distribution, and package design.

## Sunday, February 6th 8:00 AM

### T3: RF MEMS: Devices, Circuits and Packaging

RF MEMS devices including micromechanical switches, resonators, 3D high-Q inductors and micromachined antennas can enable ultra-low-power wireless architectures in ultra-small microsystems. High-Q micromechanical resonators in the VHF and UHF range have become available, and wafer-level-packaged MEMS switches have demonstrated reliable operation for billions of cycles. This tutorial presents an introduction to RF MEMS devices, reviews the latest advances in the field, and discusses their manufacturing, performance and packaging.

Instructor: Farrokh Ayazi is an Assistant Professor in the School of ECE at Georgia Tech. He received his BSEE from the University of Tehran, in 1994, and MSEE and PhD degrees from the University of Michigan, in 1997 and 2000, respectively. His research interests are in the areas of micro-/nano-electromechanical resonators, RF MEMS, VLSI Analog IC's, MEMS inertial sensors and packaging. He is a 2004 recipient of the NSF CAREER Award, the 2004 Richard M. Bass Outstanding Teacher Award, and the Georgia Tech College of Engineering Cutting Edge Research Award for 2001-2002. He has served on the technical program committees of the IEEE ISSCC, MEMS, and Sensors conferences.

### T4: PHASE-CHANGE MEMORY

Phase-change memory (PCM, also called OUM or PRAM), is an emerging non-volatile-memory technology that has the potential to improve the performance compared to Flash - write throughput (versus NOR), random read access time and throughput (versus NAND, direct write, bit granularity, endurance) - and to be scalable beyond Flash. The basic concepts of PCM, the memory cells, the electrical characteristics and the scaling perspective are reviewed. Key design aspects and challenges, related to the MOS-selected cell array as well as to the BJT-selected array, including examples and published results, are discussed.

Instructor: Giulio Casagrande graduated in Electronic Engineering in 1977 at the University of Padova, Italy. He joined ST Microelectronics, Milano, as a designer of EPROMs and EEPROMs and then he led the design and engineering team that developed the first generations of Flash memories in ST. He is presently Director of R&D of the Memory Products Group at ST Microelectronics, concentrating on advanced Flash design solutions for embedded applications, assessment and disruptive emerging memories, CAD and design methodology. He is a member of ISSCC Memory Sub-Committee.

### TOTOTILALO

# T5: DSP CIRCUIT TECHNOLOGIES FOR THE NANOSCALE ERA

Some of the sub-65nm scaling challenges and new paradigm shifts in next-generation DSP architectures are discussed. Emerging trends in wireless and embedded DSP industry including special-purpose multimedia/communication accelerators, co-processor arrays, and reconfigurable DSP engines are reviewed. Energy-efficient arithmetic and logic circuit techniques, static/dynamic supply scaling, and multi-supply/multi-threshold design for switching and leakage energy reduction are described. Dedicated hardware accelerators and data-path building blocks for enabling high MOPS/W in specialized DSP tasks are presented. Many chip design examples and their results/trade-offs are be shown as part of this tutorial.

Instructor: Ram Krishnamurthy is a Senior Staff Research Engineer at Intel Corporation's Circuit Research Laboratories in Hillsboro, OR, where he leads the high-performance and low-voltage circuits research group. He holds 41 patents issued and published over 75 papers. He serves on the SRC ICSS task force and the ISSCC, CICC, and SoC program committees. Since 1999 he serves as an adjunct faculty member at Oregon State University, where he teaches VLSI system design. He received his PhD from Carnegie Mellon University in 1998

#### T6: NANOTECHNOLOGY 101

This tutorial provides the attendee with an introduction to the emerging opportunities in novel nanoscale devices and fabrication techniques with particular emphasis on the implications for circuit and system designers. Topics covered include: fundamentals of device physics and materials science at the nanoscale, the ITRS emerging research devices (memory & logic), nanotubes, nanowires, and nanoparticles, molecular devices, and nanofabrication techniques and their impact on device layout. An assessment of the level of maturity for the proposed devices will be given.

**Instructor: H.-S. Philip Wong** joined the IBM T. J. Watson Research Center, Yorktown Heights, NY, in 1988. While at IBM Research, he was a Senior Manager having the responsibility of shaping and executing IBM's strategy on nanoscale science and technology and semiconductor technology. In September, 2004, he joined Stanford University as a Professor of Electrical Engineering.

## Sunday, February 6th 8:00 AM

# T7: POLAR MODULATORS FOR LINEAR WIRELESS TRANSMITTERS

As spectral efficiency becomes increasingly important, most emerging wireless standards apply both amplitude and phase modulation and therefore require linear modulators. Polar modulators can produce more spectrally pure signals with higher power efficiency than traditional linear modulators. This tutorial provides an introduction to the concept of polar modulation and an in-depth look at some of the implementation challenges. The following topics are covered at both system and circuit levels:

- (1) An overview of linear wireless transmitters

- (2) Polar modulator implementation, including impairment mechanisms and limitations are detailed.

- (3) Case studies of practical modulators for EDGE are treated

Instructor: Antonio Montalvo has been the director of Analog Devices Design Center in Raleigh, NC, since 2000. He is also an Adjunct Professor at North Carolina State University. He was with Ericsson from 1995 to 2000 where he led the RF IC group and with Advanced Micro Devices from 1987 to 1991 where he was involved with the design of Flash memories. He received a PhD from North Carolina State University in 1995, an MSEE from Columbia University in 1987 and a BS Physics from Loyola University in 1985.

# T8: HIGH-SPEED ELECTRICAL INTERFACES: STANDARDS AND CIRCUITS

The physical-level standard specification space (including standards under development) and challenges in multi-gigabit range high-speed electrical interfaces area, such as XFI, CEI , XAUI, Fiber-Channel, SAS, SATA, etc. are reviewed. Jitter requirements, signal amplitude, impedance, S-parameter specifications and transmission channel representation, along with equalization techniques, are studied. Block diagrams and circuit solutions are also discussed. This tutorial helps to understand IC design parameters, their link to standard specifications, and current and future challenges in wireline design for multi-gigabit electrical interfaces.

Instructor: Yuriy M. Greshishchev, is a Technical Advisor on high-speed circuit design for wireline communications at PMC Sierra, Ottawa, Canada,. His design experience is in multi-gigabit rate CMOS, SiGe, III-V circuits for telecommunications and data communications applications area. He has been involved in XFI, fiber channel, SAS, RIO physical level standard technical groups. Yuriy is a member of ISSCC Technical Program Committee for five consecutive years. He presented an ISSCC Tutorial on "Front-end Circuit Design for Optical Communications" in 2001. He has co-authored two books and numerous technical papers on the area of high-speed communication circuit design and data converters. He received his PhD degree in Electrical and Computer Engineering from V.M. Glushkov Institute of Cybernetics, Microelectronics Division, Kiev, Ukraine, in 1984.

# F1

**Clock and Frequency Generation for Wireline**

and Wireless Apllications

(Salon 9)

Organizer: Rudolf Koch, Infineon, Munich, Germany

Committee: Franz Dielacher, Infineon, Villach, Austria

Trudy Stetzler, Texas Instruments, Stafford, TX

Charles Chien, SST Communications,

Santa Monica, CA

John Long, Delft University of Technology,

Delft, The Netherlands

Roger Minear, Agere Systems, Wyomissing, PA Takehiko Nakao, Toshiba, Kanagawa, Japan

Tom Schiltz, Linear Technology,

Colorado Springs, CO

The quality of the spectrum of clock generators has a crucial impact on the performance of communications systems. Different system concepts may yield widely disparate specifications for VCOs and PLLs even for the same application.

Trade-offs between contradictory requirements, such as low phase noise and wide bandwidth, are needed to fulfill and optimize system specifications.

The morning sessions of this forum deal with fundamental aspects of frequency generation. The first two speakers treat design criteria for clock generation for wireless and wireline systems. The modeling of noise sources in oscillator circuits is addressed by the next three presenters.

In the afternoon sessions, each of the three speakers discusses analysis and design of PLL frequency synthesizers, fractional-N frequency synthesizers, and spread-spectrum PLLs for communication applications.

Finally, at the end of the afternoon, the speakers will assemble in a panel format to field questions and comments from the audience.

## Sunday, February 6<sup>th</sup> 8:00 AM

## Forum Agenda:

| <u>Time</u> | <u>Topic</u>                                                                                                                                                               |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:00        | Continental Breakfast                                                                                                                                                      |

| 8:30        | Welcome and Introduction Rudolf Koch, Infineon, Munich, Germany                                                                                                            |

| 08:35       | Formulating Design Criteria for Frequency Generation for Wireless Applications Derek Shaeffer, Aspendos Communications, San Jose, CA                                       |

| 09:05       | Formulating Design Criteria for Clock Generation for Wireline Applications Takehiko Nakao, Toshiba, Kanagawa, Japan                                                        |

| 09:35       | Multiphase Ring Oscillators and Oscillator Phase<br>Noise Modelling Techniques<br>Robert Renninger, Agere, Allentown, PA                                                   |

| 10:05       | Break                                                                                                                                                                      |

| 10:35       | VCO Design and Phase Noise Modelling Ali Hajimiri, California Institute of Technology, Pasadena, CA                                                                        |

| 11:35       | Supply and Substrate Noise in VCOs<br>Jan Craninckx, IMEC, Leuven, Belgium                                                                                                 |

| 12:05       | Lunch                                                                                                                                                                      |

| 1:30        | System Analysis, Simulation, Design and Optimization of<br>PLL Frequency Synthesizers for Communication Systems<br>Cicero Vaucher, Phillips, Eindhoven,<br>The Netherlands |

| 2:30        | Design, Simulation, and Bandwidth Extension Methods<br>for Fractional-N Frequency Synthesis<br>Michael Perrott, Massachsetts Institute<br>of Technology, Cambridge, MA     |

| 3:30        | Break                                                                                                                                                                      |

| 4:00        | Spread Spectrum PLLs; Direct Modulation with Wideband PLLs Ivan Bietti, STMicroelectronics, Pavia, Italy                                                                   |

| 5:00        | Panel Discussion                                                                                                                                                           |

| 5:30        | Conclusion                                                                                                                                                                 |

F2: Advanced Dynamic Memory Design

(Salon 7)

Organizer/Chair: Committee:

Katsuyuki Sato, Elpida., Tokyo, Japan Jinyong Chung, POSTECH, Pohang, Korea Young-Hyun Jun, Samsung, HwaSung, Korea Terry Lee, Micron Technology, Boise, ID John Barth, IBM, Essex Junction, VT Martin Brox, Infineon, Munich, Germany Takayuki Kawahara, Hitachi, Tokyo, Japan

DRAM is widely used not only as the main memory in PCs and servers, but also as the active memory in consumer products such as digital cameras, TVs, and mobile phones. Consequently, cost reduction is a paramount design consideration. Each new generation of DRAM has applied finer-pattern technology to cut costs. In this sense, new DRAM designs are leading-edge- technology-driven. This forum informs the audience about current DRAM technology and its associated circuit issues.

Jinyong Chung provides an overview of DRAM architecture, from basic cell operation to a chronological evolution of cell configuration. Cell leakage, soft errors related to alpha and neutron particles, and bit-line coupling are treated. Test-time-reduction methods to screen defective cells are described, and redundancy techniques to replace defective cells, rows or columns are developed. Size and voltage issues associated with further scaling are also discussed.

High-speed DRAM architecture and design is the focus of the second talk by Young-Hyun Jun. The key to high-speed operation is the internal clock-generation process in which DLLs and PLLs are vital. From basic circuit concepts to current practice, DLL and PLL design issues are discussed. The application of DLL and PLL techniques in graphics RAM and DDR2 are among the products illustrated. The new technologies needed to realize future high-speed DRAMs are presented.

The DRAM I/O interface is the subject of the talk by Terry Lee. Cost minimization, test-time reduction, the test of multiple devices in parallel, low-power multi-drop busses and upgradability are among the critical features needed in DRAM applications. This causes DRAM I/O to differ from data communications and backplane signaling. The theme of this presentation is the circuit and system design issues related to high-speed DRAM interfaces.

On-chip SRAM cache density is restricted by the limitations in SRAM size. High-performance embedded DRAM is aimed at applications employing on-chip cache. John Barth describes the technology of embedded DRAM to realize high speed and a wide internal bus with a minimum die penalty while suppressing noise. Structures for high-speed embedded DRAM testing are described, and design-for-test techniques are introduced.

Martin Brox focuses on DRAM for mobile applications including browsers, cameras, and video-conferencing. These all require high-density DRAMs. The talk treats the design of mobile RAM to meet the unique requirements necessitated by such applications.

## Sunday, February 6th 8:00 AM

Takayuki Kawahara introduces the design of sub-1V DRAMs which play critical roles in reducing dissipation in MPU/SoC/SiP for power-aware systems. However, four major challenges need be faced to achieve this: reducing leakage currents; maintaining the signal charge of memory cells; reducing speed variations caused by deviations of threshold voltage, and reducing the cell size. He presents current advances to deal with these issues in sub-1V DRAMs, and solutions for nanoscale LSI system.

Tomoyuki Ishii introduces future challenges for DRAM technology in the nanoscale process generation. From an operational-stability point-of-view, DRAM has better scalability than SRAM. However, the standard 1T1C type DRAM has serious difficulties in maintaining adequate retention time and storage capacitance, as the process scales. Several non-1T1C approaches for scalable DRAM are introduced, along with new device structures. Investigation of a memory cell using only 10 electrons per bit is discussed.

### Forum Agenda:

| <u>Time</u> | <u>Topics</u>                                                                             |

|-------------|-------------------------------------------------------------------------------------------|

| 8:00        | Continental Breakfast                                                                     |

| 8:30        | Introduction & Updates Jinyong Chung, POSTECH, Pohang, Korea                              |

| 9:15        | High-Speed DRAM Design<br>Young-Hyun Jun, Samsung, HwaSung, Korea                         |

| 10:15       | Break                                                                                     |

| 10:30       | DRAM I/O Interface<br>Terry Lee, Micron Technology, Boise, ID                             |

| 11:30       | High Performance Embedded DRAM and test structures<br>John Barth, IBM, Essex Junction, VT |

| 12:30       | Lunch                                                                                     |

| 1:15        | DRAM Design for Mobile Applications Martin Brox, Infineon, Munich, Germany                |

| 2:15        | Sub-1V DRAM Design<br>Takayuki Kawahara, Hitachi, Tokyo, Japan                            |

| 3:15        | Break                                                                                     |

| 3:30        | DRAM in Nanoscale Era<br>Tomoyuki Ishii, Hitachi, Tokyo, Japan                            |

| 4:30        | Conclusion                                                                                |

### SPECIAL-TOPIC EVENING SESSIONS

SE1: Powerline LAN: Is There a Concrete Wall Dividing Wireless

from Wireline?

(Salon 8)

Organizer: Mark Ingels, STMicroelectronics

Zaventem, Belgium

Chair: Michael Green, University of California, Irvine, CA

From offices to coffee houses, wireless LANs have become ubiquitous within the United States. However, there are many situations where a wireless signal encounters attenuation within a building. For example concrete walls and ceilings are known to impede RF transmission. In such situations Power Line Communication (PLC) is emerging as an alternative technology for high-speed data communication within the home. This new technology can assist or even replace the wireless systems as needed. In this Special-Topic Evening session, the significance of PLC will be revealed. Infrastructural aspects that may affect the choice between wireline and wireless for the transmission of broadband data is addressed and the advantages and needs for powerline systems is demonstrated. The session gives an overview and comparison of various available and emerging PLC technologies and practical systems are presented.

## Sunday, February 6th 7:30 PM

SE1: Powerline LAN: Is There a Concrete Wall Dividing Wireless from Wireline?

| <u>Time</u> | <u>Topics</u>                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:30        | Broadband Powerline Multimedia Home Networking:<br>Advantages and Challenges,<br>Haniph A. Latchman, University of Florida<br>Gainesville, FL |

| 8:00        | OFDM for Powerline Communications Jim Petranovich, Conexant Systems, San Diego, CA                                                            |

| 8:30        | Performance Analysis of a CDMA Chipset for InHouse<br>Broadband Powerline Communications,<br>Vincent Buchoux, LEA, Courbevoie, France         |

| 9:00        | Remote Control via Powerline,                                                                                                                 |

## SPECIAL-TOPIC EVENING SESSIONS

SE2: When Processors Hit the Power Wall (or "When the CPU hits the fan").

(Salon 7)

Organizer: Sam Naffziger, Hewlett Packard, Fort Collins, CO

CO - Organizer: James Warnock, IBM, Yorktown Heights, NY CO - Organizer: Herbert Knapp, Infineon, Munich, Germany

Power consumption and heat removal have become first-order limiters to "Moore's Law" in regards to the growth of processor performance. This limitation has bubbled up from mobile devices to desktop systems and now even server processors are investing heavily in techniques that manage and reduce power consumption. The result is a fundamental shift in how circuit designers and architects attempt to achieve performance from each new design generation. No aspect of the processor design ecosystem goes untouched: silicon process technology, circuit design, computer architecture, packaging and cooling are all facing fundamental shifts in pri-orities and methods. The power consumption problem on leading edge processors and the possible technology directions in architecture, circuits and cooling are explored in this special-topics session. The first step to solving a problem is to understand it better by identifying it. So we begin by examing where the power is consumed on a leading edge processor and how it varies with time and workload. The next talk involves a look at one of the frontiers of VLSI design: the many opportunities present in creating "environmentally aware" chips that measure and react to their environment to optimize power, performance and other tradeoffs. Lastly two of the industries leading architects discuss the meaning of "low-power architecture", and some of the brightest opportunities for power efficiency. The session concludes with a look by one of the leading innovators in cooling technology at how waste heat that byproduct of computation can be removed efficiently.

| <u>Time</u> | Topic                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| 7:30 pm     | Spatially Resolved Imaging Of Microprocessor Power<br>Hendrik Hamann, IBM, Yorktown Heights, NY                 |

| 8:00 pm     | Adaptive Techniques for Managing Power Consumption Takayasu Sakurai, University of Tokyo, Tokyo, Japan          |

| 8:30 pm     | Low-Power for High-Performance PC Compatible Processors David R. Ditzel, Transmeta Corporation, Santa Clara, CA |

| 9:00 pm     | Power-Efficient Stream Architectures William Dally, Stanford University and Stream Processors, Palo Alto, CA    |

| 9:30 pm     | Advanced Cooling for High Performance VLSI<br>Ken Goodson, Stanford University, Palo Alto, CA                   |

## Sunday, February 6th 7:30 PM

SE3: Integration in the 3rd Dimension: Opportunities and Challenges

(Salon 9)

Organizer: Larry Pileggi, Carnegie Mellon University, Pittsburgh, PA

Chair: Werner Weber, Infineon, Munich, Germany

While it is apparent that integrating electronic systems beyond two dimensions can potentially provide great advantages, it is less obvious what the most promising approaches for such integration will be with future technologies. The papers in this session will describe and evaluate various opportunities and challenges for vertical integration of integrated electronic systems. Cost considerations are considered prominently, as well as the potential performance improvements that are realized. Various integration concepts are considered for integrated systems which include digital logic, analog circuits and sensors. The session begins with a cost-based argument for 2.5D integration based on stacking of traditional 2D integrated circuits. Results indicate a performance advantage as well due to the shortening of long interconnect wiring when integrating in 3D. A subsequent paper applies similar performance reasoning for "folding" ICs into multiple active layers to reduce the lateral dimensions. Exciting opportunities are further explored for expanding in the 3rd dimension via RF-MEMS components that are built directly on top of monolithic ICs. Then, the session closes with a description of how wafer-scale integration in the third dimension is used to construct antennas and other microwave components that would otherwise be challenging, if not impossible, for traditional monolithic design.

####

of 2.5-D Integration

Wojciech Maly, Carnegie Mellon University,

Pittsburgh, PA

- 8:00 3D Integration's Architectural and

Circuit Design Opportunities

Wilfried Haensch, IBM, Yorktown Heights NY

- 8:30 Above IC & embedded RF MEMs platform for SoC Integration: Status and Prospect Pascal Ancey, STMicroelectronics, Crolles Cedex, France

- 9:00 A Wafer Level Integration Technology for On-Wafer Antennas and Microwave Components

Hermann Schumacher, University of Ulm,

Ulm, Germany

### OLOGION I OALON I

### PLENARY SESSION - INVITED PAPERS

Chair: Timothy Tredwell, Eastman Kodak, Rochester, NY

ISSCC Executive-Committee Chair

Associate Chair: lan Young, Intel, Hillsboro, OR

ISSCC Program-Committee Chair

#### FORMAL OPENING OF THE CONFERENCE

8:30AM

### 1.1 Nanoelectronics for the Ubiquitous Information Society

8:40AM

Daeje Chin, Minister of Information and Communications, Korea

Nanoelectronics will open up both new opportunities and new challenges. Meanwhile, it has been successfully used in mass production of gigabit memories, including Flash and DRAM, and in field-emission display (FED) with carbon nano-tubes. The technical challenge is to deal with process and device parameter variation, while the economic challenge is to reduce the high cost of fabrication. One way to overcome these technical and economic uncertainties is to organize a tight collaboration of the device industry with system and service industries, to distribute the risk, and to maximize the total social benefit. The "IT 839 Strategy" of the Korean Government is an example of such a program to enhance cooperation amongst service, system, and device industries, to speed up the use of nanoelectronics for the realization of a ubiquitous information society. In such a society, information technology (IT) enables everyone to enjoy daily life without awareness of IT itself. This is made possible by the "Invisible Silicon" that resides within almost everything in our society, to sense, analyze, and control ourselves and our environment. Nanoelectronics allows the mass production of such new silicon. RFID chips and sensor networks are examples of "Invisible Silicon", which will integrate nano-electro-mechanical systems and RF technology, as well as low-power and multi-media SoCs. These technologies will facilitate future IT, and change our world, just as fourth-generation mobile-phone developments are leading us to the ubiquitous information society.

### ISSCC, SSCS, JSSCC, & IEEE AWARD PRESENTATIONS

9:30AM

**BREAK 10:00 AM**

#### 1.2 Ambient Intelligence: Broad Dreams and Nanoscale Realities

10:15AM

Hugo De Man, Senior Research Fellow, IMEC; Professor, Katholieke Universiteit Leuven, Belgium

Ambient Intelligence (AmI) is a vision of a world in which people will be surrounded by networks of intelligent devices that are sensitive to, and adaptive to, their needs. This concept implies a consumer-oriented industry driven by software from the top, and enabled (and constrained) by nano-scale physics at the atomic level. "more-Moore" will be needed to deliver the Giga-ops computation and GHz communication capabilities required for stationary and wearable devices. But AmI also creates new challenges at the architectural and physical levels. To make AmI possible, AmI devices need two-orders-of-magnitude-lower power dissipation than

## Monday, February 7th 8:30 AM

today's microprocessors, at one-twentieth of the cost. But these requirements conflict with the embedded programmability needed for personalization and adaptation to new services. We will focus on emerging techniques for bridging this gap between software-centric systems and power-efficient platform architectures for Aml devices.

A second challenge is to cope with the fact that nano-scale physical phenomena are in conflict with the traditional "nice and predictable" digital abstractions now used for complexity management. Techniques for coping with uncertainty and signal degradation, while achieving better-than-worst-case design, will be discussed.

Finally, one must realize that to facilitate Aml, "more-than-Moore" technology is required, for example, for the design of autonomous wireless sensor networks. Correspondingly, attention will be paid to novel combinations of technologies above and around CMOS, for the design of ultra-low-power, ultra-simple sensor motes for Aml.

# 1.3 Innovation and Integration in the Nanoelectronics Era 11:05AM

Sunlin Chou, Senior Vice President and General Manager, Technology and Manufacturing Group, Intel, Hillsboro, OR

Demand for electronics continues to grow as new products combine and enhance computing, communications, and digital capabilities. Hardware and software are evolving to enable new applications and usage modes, by offering features such as multitasking, parallel processing, mobility and wireless connectivity. Integration at both component and product platform levels, and efficient use of power, will become more important. These call for holistic solutions involving systems, circuits, processes, devices, and packaging. Many techniques to improve power efficiency have been developed and more will emerge. Silicon technology and scaling remain keys to progress, with transistors and circuit elements already at nanoscale dimensions. Innovation will accelerate as nanotechnology further renews and extends silicon technology. Skillful integration of new materials, processes, and device structures will be essential. Successful nanoelectronics companies will excel in innovation and integration, extend Moore's Law into and beyond the next decade, and drive the development of future growth opportunities.

### SESSION 2 SALON 1-6

#### NON-VOLATILE MEMORY

Chair: Yair Sofer, Saifun Semiconductors, Netanya, Israel Associate Chair: Yukihito Oowaki, Toshiba, Kawasaki, Japan

#### 2.1 A 146mm<sup>2</sup> 8Gb NAND Flash Memory in 70nm CMOS

1:30 PM

T. Hara', K. Fukuda', K. Kanazawa', N. Shibata', K. Hosono', H. Maejima', M. Nakagawa', T. Abe', M. Kojima', M. Fujiu', Y. Takeuchi', K. Amemiya', M. Morooka', T. Kamer, H. Nasu', K. Kawano', C-M. Wang', K. Sakurai', N. Tokiwa', H. Waki', T. Maruyama', S. Yoshikawa', M. Higashitani', T. Pham'

<sup>1</sup>Toshiba, Yokohama, Japan <sup>2</sup>SanDisk, Yokohama, Japan

3SanDisk, Sunnyvale, CA

A 146mm² 8Gb NAND flash memory with 4-level programmed cells is fabricated in a 70nm CMOS technology. A single-sided pad architecture and extended block-addressing scheme without redundancy is adopted for die size reduction. The programming throughput is 6MB/s and is comparable to binary flash memories.

# 2.2 An 8Gb Multi-Level NAND Flash Memory in a 63nm CMOS Process

2:00 PM

D-S. Byeon, S-S. Lee, Y-H. Lim, J-S. Park, W-K. Han, P-S. Kwak, D-H. Kim, D-H. Chae, S-H. Moon, S-J. Lee, H-C. Cho, J-W. Lee, J-S. Yang, Y-W. Park, D-W. Bae, J-D. Choi, S-H. Hur, K-D. Suh Samsung, Hwasung, Korea

An 8Gb multi-level NAND flash memory is fabricated in a 63nm CMOS technology with shallow trench isolation. The cell and chip sizes are  $0.02\mu m^2$  and  $133mm^2$ , respectively. Performance improves to 4.4MB/s by using the 2x program mode and by decreasing the cycle time from 50ns to 30ns. This also improves the read throughput to 23MB/s.

# 2.3 Enhanced Write Performance of a 64Mb Phase-Change RAM

H-R. Oh, S. KANG, B. Cho, W. Cho, B-G. Choi, H. Kim, K-S. Kim, D-E. Kim, C-K. Kwak, H-G. Byun Samsung, Hwasung, Korea

A 1.8V 64Mb Phase-Change RAM with improved write performance is fabricated in a 0.12 $\mu m$  CMOS technology. The improvement of RESET and SET distributions is based on cell current regulation and multiple step-down pulse generators. The read access time and SET-write time are 68ns and 180ns, respectively.

**BREAK 3:00 PM**

#### Monday, February 7<sup>th</sup> 1:30 PM

#### 2.4 A 128Mb NOR Flash Memory with 3MB/s Program Time and Low-Power Write Using an In-Package Inductor Charge-Pump

3:15 PM

R. Sundaram, J. Javanifard, P. Walimbe, B. Pathak, R. Melcher, P. Wang, J. Tacata Intel, Folsom, CA

Improved performance of flash memories requires programming more cells in parallel. This design uses an inductive pump to transfer the energy to a capacitor to achieve the needed voltage. The discrete inductor is bonded atop the die which also includes the control circuitry. With an inductive pump, the current saving in the program mode is 47.5mA compared to a capacitive pump.

#### 2.5 A 125MHz Burst-Mode Flexible Read-While-Write 256Mb **NOR Flash Memory**

3:45 PM

- C. Villa', D. Vimercati', S. Schippers', E. Confalonieri', M. Sforzin', S. Polizzi', M. La Placa', C. Lisi', A. Magnavacca', E. Bolandrina', A. Martinelli', V. Dima', A. Scavuzzo', B. Calandrino', N. Del Gatto', M. Scardaci', F. Mastroianni', M. Pisasale', A. Geraci', M. Gaibotti', M. Sali1

- <sup>1</sup>STMicroelectronics, Agrate Brianza, Italy

- <sup>2</sup>STMicroelectronics, Palermo, Italy

- 3STMicroelectronics, Catania, Italy

A 1.8V 256Mb 2b/cell NOR flash memory is designed in a 130nm technology. A fast gate-voltage-ramp constant-current-reading concept is implemented to obtain a robust read-while-write/erase function and 125MHz burst read frequency.

#### A 90nm 512Mb 166MHz Multi-Level Cell Flash with 2.6 1.5MB/sProgramming

4:15 PM

M. Taub', R. Bains', H. Castro', S. Eilert'. R. Fackenthal', C. Haid', K. Parat', S. Peterson', A. Proescholdt', K. Ramamurthi', P. Ruby', M. Szwarc<sup>1</sup>, D. Young<sup>1</sup> <sup>1</sup>Intel, Foslom, CA <sup>2</sup>Intel. Santa Clara. CA

A 2b/cell flash memory in 90nm triple-well CMOS technology achieves 1.5MB/s programming and 166MHz synchronous operation. The design features 2-row programming, optimized program control hardware, 3 transistor x-decoder with negative deselected rows and configurable output buffers. The die is 42.5mm² with a cell size of 0.076μm².

#### 126mm<sup>2</sup> 4Gb Multi-Level AG-AND Flash Memory 2.7 with 10MB/s Programming Throughput

4:45 PM

H. Kurata<sup>a</sup>, Y. Sasago<sup>a</sup>, K. Otsuga<sup>a</sup>, T. Arigane<sup>a</sup>, T. Kawamura<sup>a</sup>, T. Kobayashi<sup>a</sup>, H. Kume<sup>a</sup>, K. Homma<sup>a</sup>, K. Kozakai<sup>a</sup>, S. Noda<sup>a</sup>, T. Ito<sup>a</sup>, M. Shimizu<sup>a</sup>, Y. Ikeda<sup>a</sup>, O. Tsuchiya<sup>a</sup>, K. Furusawa<sup>a</sup>

<sup>1</sup>Hitachi, Kokubunji, Japan

<sup>2</sup>Hitachi, Tokyo, Japan

3Renesas Technology, Tokyo, Japan

A 4Gb flash memory, fabricated in 90nm CMOS technology, results in a 126mm² chip size and a 0.0162µm²/b cell size. Address and temperature compensation methods control the resistance of the inversion-layer local bit-line. Programming throughput of 10MB/s is achieved by using self-boosted charge injection scheme.

**CONCLUSION 5:15 PM**

### SESSION 3 SALON 7

#### **BACKPLANE TRANSCEIVERS**

Chair: Mehmet Soyuer, IBM, Yorktown Heights, NY Associate Chair: Muneo Fukaishi, NEC, Kanagawa, Japan

# 3.1 A 5Gb/s NRZ Transceiver with Adaptive Equalization for Backplane Transmission

1:30 PM

N. Krishnapura, M. Barazande-Pour, Q. Choudhry, J. Khoury, K. Lakshimikumar, A. Aggarwal

Vitesse Semiconductor, Somerset, NJ

The proposed 5Gb/s transceiver has a transmitter with 2-tap pre-emphasis and an adaptive receiver with 1-tap feedforward and 3-tap decision feedback equalization. The quad transceiver occupies 12mm² in 0.13µm CMOS, consumes 2.1W from 1.2V, and has a BER <10<sup>-15</sup> over 4 pairs of 1-meter backplane trace with crosstalk.

# 3.2 A 6.4Gb/s CMOS SerDes Core with Feedforward and Decision-Feedback Equalization

2:00 PM

M. Sorna¹, T. Beukema², K. Selander¹, S. Zier¹, B. Ji¹, P. Murfet٩, J. Mason³, W. Rhee², H. Ainspan², B. Parker²

<sup>1</sup>IBM, Hopewell Junction, NY

<sup>2</sup>IBM, Yorktown Heights, NY

<sup>3</sup>IBM, Hursley, United Kingdom

A 4.9 to 6.4Gb/s 2-level SerDes ASIC I/O core designed in 0.13µm CMOS uses a 4-tap FFE in the transmitter and a 5-tap DFE with receiver AGC. Error-free operation is achieved on channels with over 30dB loss at the half-baud rate. The TX/RX pair consumes 290mW from a 1.2V supply and uses a die area of 0.79mm².

# 3.3 A 0.6 to 9.6Gb/s Binary Backplane Transceiver Core in 0.13µm CMOS

2:30 PM

K. Krishna', D. Yokoyama-Martin', S. Wolfer', C. Jones', M. Loikkanen', J. Parker', R. Segelken', J. Sonntag', J. Stonick', S. Titus', D. Weinlader' 'Synopsys, Hillsboro, OR 'Stexar, Hillsboro, OR 'UNC, Chapel Hill, NC

A backplane transceiver core in 0.13 $\mu$ m dual-gate CMOS, operating at 0.6 to 9.6Gb/s with an area of 0.56mm² and dissipating 150mW at 6.25Gb/s, is presented. This core uses a unique adaptive receive equalization strategy, transmit pre-emphasis, and has extensive optional test features including a built-in BER tester and an on-chip receiver sampling scope.

BREAK 3:00PM

#### Monday, February 7th 1:30 PM

#### 3.4 A Transmit Architecture with 4-Tap Feedforward Equalization for 6.25/12.5Gb/s Serial Backplane Communications

3:15 PM

P. Landman, K. Brouse, V. Gupta, S. Wu, R. Payne, U. Erdogan, R. Gu, A-L. Yee, B. Parthasarathy, S. Ramaswamy, B. Bhakta, W. Mohammed, J. Powers, Y. Xie, L. Wu, L. Dyson, K. Heragu, W. Lee Texas Instruments, Dallas, TX

A transmit architecture with a programmable 4-tap feedforward equalizer for 6.25 to 12.5Gb/s serial communications through lossy channels is described. A 16:8-channel MUX/DEMUX chip fabricated in a 0.13µm 7M CMOS process, demonstrates a near-end jitter or 16ps and an equalized far-end jitter of 55ps at 6.25Gb/s over a 36" legacy backplane channel.

#### 3.5 A 6.25Gb/s Binary Adaptive DFE with First Post-Cursor Tap **Cancellation for Serial Backplane Communications**

R. Payne, B. Bhakta, S. Ramaswamy, S. Wu, J. Powers, B. Parthasarathy, P. Landman, U. Erdogan, A-L. Yee, R. Gu, L. Wu, Y. Xie, K. Brouse, W. Mohammed, K. Heragu, V. Gupta, L. Dyson, W. Lee Texas Instruments, Dallas, TX

A 6.25Gb/s serial receiver with a 4-tap adaptive DFE is implemented in a 0.13µm 7LM CMOS process. Direct cancellation of the first post-cursor ISI is achieved, enabling recovery of a data eye fully closed from channel losses and crosstalk. A BER<10<sup>-15</sup> is measured over legacy backplane channels.

#### 3.6 12Gb/s Duobinary Signaling with x2 Oversampled Edge Equalization

4:15 PM

K. Yamaguchi<sup>1</sup>, K. Sunaga<sup>1</sup>, S. Kaeriyama<sup>1</sup>, T. Nedachi<sup>1</sup>, M. Takamiya<sup>1</sup>, K. Nose<sup>1</sup>, Y. Nakagawa<sup>1</sup>, M. Sugawara<sup>2</sup>, M. Fukaishi<sup>1</sup> <sup>1</sup>NEC, Sagamihara, Japan

<sup>2</sup>NEC, Santa Clara, CA

A backplane transceiver in 90nm CMOS that employs duobinary signaling over copper traces is described. To introduce duobinary signaling into data transfers on printed boards, three techniques are developed: 1) edge equalization for equalizer adaptation, 2) 2x oversampled transmitter equalizer for ISI control, and 3) 2b-transition-ensure encoding for clock recovery.

#### 3.7 A 25Gb/s PAM4 Transmitter in 90nm CMOS SOI

4:45 PM

C. Menolfi<sup>1</sup>, T. Toifl<sup>1</sup>, R. Reutemann<sup>2</sup>, M. Ruegg<sup>2</sup>, P. Buchmann<sup>1</sup>, M. Kossel<sup>1</sup>, T. Morf<sup>1</sup>, M. Schmatz <sup>1</sup>IBM, Rueschlikon, Switzerland <sup>2</sup>Miromico, Zurich, Switzerland

A 25Gb/s multi-level PAM4 transmitter intended for short-range chip-tochip on-board interconnects is presented. A 4-tap FIR pre-emphasis filtering scheme is used to equalize channel loss and to improve eye opening. Fabricated in a low-k partially depleted 90nm SOI technology, it occupies 0.052mm<sup>2</sup> and draws 99.3mA from a 1V supply.

> CONCLUSION 5:15 PM

### SESSION 4 SALON 8

#### TD: MIXED-DOMAIN SYSTEMS

Chair: Kerry Bernstein, IBM, Essex Junction, VT

Associate Chair: Siva Narendra, Intel, Hillsboro, OR

# 4.1 Joining Ionics and Electronics: Semiconductor Chips with Ion Channels, Nerve Cells and Brain Tissue

1:30 PM

P. Fromherz

Max Planck Institute for Biochemistry, Munich, Germany

The microscopic interfacing of semiconductor devices and living neuronal systems is discussed. From the biological side, ion channels, nerve cells, and brain tissue are considered. Basic experimental studies are performed with capacitors and transistors of simple silicon chips. The approach is extended to a CMOS chip with 16000 transistor sensors.

### 4.2 An Analog Bionic Ear Processor with Zero-Crossing Detection

2:00 PM

R. Sarpeshkar, M. Baker, C. Salthouse, J-J. Sit, L. Turicchia, S. Zhak Massachusetts Institute of Technology, Cambridge, MA

A 75dB 251µW analog speech processor is described that preserves the performance, robustness, and programmability needed for deaf patients at a reduced power consumption compared to that of implementations with A/D and DSP. It also provides zero-crossing outputs for stimulation strategies that use phase information to improve performance.

### 4.3 An IC/Microfluidic Hybrid Microsystem for 2D Magnetic Manipulation of Individual Biological Cells

2:30 PM

H. Lee¹, Y. Liu¹, E. Alsberg², D. Ingber², R. Westervelt¹, D. Ham¹¹Harvard University, Cambridge, MA²²Harvard Medical School, Boston, MA

A microfluidic system is fabricated on top of an IC chip, suspending magnetic-bead-tagged biological cells in a biocompatible environment. The IC produces patterned magnetic fields using a microcoil array to manipulate individual bead-bound cells. The hybrid prototype manipulates bovine capillary endothelial cells with precise spatial control.

**BREAK 3:00 PM**

### 4.4 A VLSI Analog Computer/Math Co-Processor For A Digital Computer

3:15 PM

G. Cowan, R. Melville, Y. Tsividis Columbia University, New York, NY

A single-chip VLSI analog computer having 80 integrators and 336 other programmable linear and nonlinear circuits is fabricated in a 0.25µm CMOS process. The chip can be used to accelerate a digital computer's numerical routines. The IC is 1cm² and consumes 300mW.

## Monday, February 7th 1:30 PM

### 4.5 Towards Chip-Scale Atomic Clocks

3:45 PM

C. Nguyen<sup>1</sup>, J. Kitching<sup>2</sup>

<sup>1</sup>DARPA, Arlington, VA, and University of Michigan, Ann Arbor, MI

<sup>2</sup>NIST, Boulder, CO

MEMS technology is used to shrink atomic clocks from their present-day table-top sizes down to only 1cm³ while at the same time retaining timing stability on the order of 30ns over one hour. The power consumption of the system is less than 30mW.

# 4.6 Opportunities for Optics in Integrated Circuits Applications 4:15 PN

D. Miller, A. Bhatnagar, S. Palermo, A. Emami-Neyestanak, M. Horowitz Stanford University, Stanford, CA

Optics potentially addresses two key problem in electronic chips and systems: interconnects and timing. Short optical pulses (e.g., picoseconds or shorter) offer particularly precise timing. Results are shown for optical and electrical four-phase clocking, with <1ps rms jitter for the optical case.

## 4.7 Processing of MEMS Gyroscopes on Top of CMOS ICs

4:45 PM

A. Witvrouw<sup>1</sup>, A. Mehta<sup>1</sup>, A. Verbist<sup>1</sup>, B. Du Bois<sup>1</sup>, S. Van Aerde<sup>2</sup>, J. Ramos-Martos<sup>3</sup>, J. Ceballos<sup>3</sup>, A. Ragel<sup>3</sup>, J. Mora<sup>3</sup>, M. Lagos<sup>3</sup>, A. Arias<sup>3</sup>, J. Hinojosa<sup>3</sup>, J. Spengler<sup>1</sup>, C. Leinenbach<sup>5</sup>, T. Fuchs<sup>5</sup>, S. Kronmueller<sup>5</sup>

IMÉC, Leuven, Belgium

<sup>2</sup>ASM, Leuven, Belgium

<sup>3</sup>IMSE-CNM, Sevilla, Spain

<sup>4</sup>Philips Research, Boeblingen, Germany

<sup>5</sup>Bosch, Gerlingen-Schillerhoehe, Germany

Integrated 10 $\mu$ m thick poly-SiGe gyroscopes are processed on top of an 8" standard 0.35 $\mu$ m CMOS wafer with 5 metal levels by using an advanced plasma-enhanced chemical vapor deposition multi-layer technology. The gyroscopes are free-moving with Q-factors for the drive mode up to 10000 at the pressure of 0.8mTorr while the CMOS chip is fully functional.

CONCLUSION 5:15 PM

## SESSION 5 SALON 9

#### WLAN TRANSCEIVERS

Chair: Arya Behzad, Broadcom, San Diego, CA

Associate Chair: Mototsugu Hamada, Toshiba, Kawasaki, Japan

#### 5.1 An Auto-I/Q Calibrated CMOS Transceiver for 802.11g

:30 PM

Y. Hsieh', W-Y. Hu², S-M. Lin², C-L. Chen², W-K. Li², S-J. Chen¹, D. Chen² ¹National Taiwan University, Hsin-Chu, Taiwan

<sup>2</sup>Muchip, Hsin-Chu, Taiwan

3National Taiwan University, Taipei, Taiwan

The CMOS transceiver IC uses the super-heterodyne architecture to implement a 802.11g RF front-end with auto I/Q calibration function.  $1^{\circ}$  quadrature mismatch and 0.1dB gain mismatch can be achieved after the auto tuning in both the transmitter and receiver sides. Implemented in a 0.25 $\mu m$  CMOS process with 2.7V supply, the transceiver achieves a 5.1dB receive cascade NF and a 7dBm transmit output  $P_{1dB}$ .

### 5.2 An 802.11g WLAN SoC

2:00 PM

S. Mehta', D. Weber', M. Terrovitis', K. Onodera', M. Mack', B. Kaczynski', H. Samavati', S. Jen', W. Si', M. Lee', K. Singh', S. Mendis', P. Husted', N. Zhang', B. McFarland', D. Su', T. Meng', B. Wooley<sup>c</sup> 'Atheros Communications, Sunnyvale, CA 'Stanford University, Stanford, CA

A single-chip 802.11g-compliant WLAN radio that implements all RF, analog, and digital PHY and MAC functions is implemented in a 0.18µm CMOS technology. The IC transmits 4dBm EVM-compliant output power for a 64QAM OFDM signal. The overall receiver sensitivities are -95dBm and -73dBm for data rates of 6Mb/s and 54Mb/s, respectively.

#### 5.3 A Fully Integrated SoC for 802.11b in 0.18μm CMOS

2:30 PM

H. Darabi, S. Khorram, Z. Zhou, T. Li, B. Marholev, J. Chiu, J. Castaneda, E. Chien, S. Anand, S. Wu, M. Pan, H. Kim, P. Littieri, B. Ibrahim, J. Rael, L. Tran, E. Geronaga, J. Trachewsky, A. Rofougaran Broadcom, Irvine, CA

A 0.18 $\mu$ m CMOS 802.11b SoC integrated all the radio building blocks including the PA, the PLL loop filter, and the antenna switch, as well as the complete physical layer and the MAC sections. At 2.4GHz, it dissipates 165mW in the receive-mode and 360mW in the transmit-mode from a 1.8V supply. The receiver achieves a typical NF of 6dB, and -88dBm sensitivity at 11Mb/s rate. The transmitter delivers a nominal output power of 13dBm.

**BREAK 3:00 PM**

### 5.4 A Compact Dual-Band Direct-Conversion CMOS Transceiver for 802.11a/b/g WLAN

3:15 PM

Z. Xu¹, S. Jiang¹, Y. Wu¹, H-Y. Jian¹, G. Chu¹, K. Ku¹, P. Wang¹, N. Tran¹, Q. Gu¹, M-Z. Lai¹, C. Chien¹, M. Chang¹², P. Chow¹¹SST Communications, Santa Monica, CA²University of California, Los Angeles, CA

A dual-band direct-conversion RF transceiver for 802.11a/b/g WLAN is implemented in  $0.18\mu m$  CMOS technology with  $6mm^2$  die size and 182mW power dissipation while transmitting 1dBm at 5GHz. The receiver achieves 5dB NF, -8dBm IIP3 (high LNA gain), 96dB total gain, and -31.4dB EVM. The transmitter achieves 1dBm and 2.5dBm linear output power at 5GHz and 2.4GHz, respectively, with an EVM less than -31dB.

## Monday, February 7th 1:30 PM

# 5.5 A Low-Power Dual-band Triple-Mode WLAN CMOS Transceiver

3:45 PM

T. Maeda, T. Yamase, T. Tokairin, S. Hori, R. Walkington, K. Numata, N. Matsuno, K. Yanagisawa, N. Yoshida, H. Yano, Y. Takahashi, H. Hida SNEC, Tsukuba, Japan

The 0.18µm CMOS direct-conversion dual-band triple-mode WLAN transceiver covers 2.4 to 2.5GHz and 4.9 to 5.95GHz and draws 78mA in the receive mode and 76mA in the transmit mode, from a 1.8V supply both at 2.4/5GHz. The system NF of 3.5/4.2dB, the sensitivity of -93/-94dBm for a 6Mb/s OFDM signal, and the EVM of 3.2/3.4% are obtained at 2.4/5.2GHz.

### 5.6 An SoC for Bidirectional Point-to-Multipoint Wireless Digital Audio Applications

4:15 PM

K. Kianush<sup>1</sup>, J. Rapp<sup>2</sup>, D. Westberg<sup>2</sup>, J. van Valburg<sup>3</sup>, P. Johansson<sup>2</sup>, R. Ponnette<sup>4</sup>, N. Philips<sup>4</sup>

<sup>1</sup>Catena, Delft, The Netherlands

<sup>2</sup>Catena, Kista, Sweden

3Catena, Eindhoven, The Netherlands

<sup>4</sup>Philips, Leuven, Belgium

A single-chip transceiver for wireless digital audio applications is realized in a  $0.25\mu m$  BiCMOS process. To avoid the congested 2.4GHz band and to achieve better penetration through walls, 863 and 915MHz bands are adopted. The frame structure used in this design guarantees a low latency for streaming audio. Adaptive frequency hopping and antenna diversity ensure robust link management.

# 5.7 A Dual-Band Frequency Synthesizer for 802.11a/b/g with Fractional-Spur Averaging Technique

4:45 PM

S. Pellerano, S. Levantino, C. Samori, A. Lacaita Politecnico di Milano, Milan, Italy

A 0.25 $\mu$ m BiCMOS spur-compensated fractional-N PLL is implemented in an 802.11a/b/g zero-IF transceiver. The synthesizer covers the 2.4 to 2.5GHz and the 5.1 to 5.9GHz bands with 0.5MHz and 5MHz resolution, respectively. The phase noise integrated from 10kHz to 10MHz is lower than 1.25° rms for any synthesized carrier. The power consumption is 39/59mW in 2.5/5GHz mode from 2.5V supply.

### 5.8 A Fully Integrated Transformer-Based Front-End Architecture for Wireless Transceivers

5:00 PM

I. Bhatti, R. Roufoogaran, J. Castaneda Broadcom, Irvine, CA

A fully integrated transformer-based RF front-end architecture is presented that integrates matching, combining, and T/R switch functions on chip. The front-end is implemented in a  $0.18\mu m$  CMOS Bluetooth transciever achieving -90dBm receiver sensitivity and 2dBm transmit power from a 1.8V supply.

**CONCLUSION 5:15 PM**

## SESSION 6 SALON 10-15

#### HIGH-SPEED AND OVERSAMPLED DACS

Chair: Robert Neff, Agilent Technologies, Palo Alto, CA Associate Chair: Zhongyuan Chang, IDT-Newave Technology,

Shanghai, China

### 6.1 A 1.2GS/s 15b DAC for Precision Signal Generation

1:30 PM

R. Jewett, J. Liu, K. Poulton Agilent Technologies, Palo Alto, CA

A 1.2GS/s 15b DAC achieves untrimmed SFDR of -70dBc to  $f_s/4$  and -63dBc to Nyquist (with 10dB better results at 500MS/s). A per-element resampling scheme and dynamic element matching achieve DNL of 2LSBs. In RZ output mode, ACPR for a 20MHz band at 900MHz is 69dB. The chip uses  $40\text{GHz-}f_{\text{T}}$  NPNs and is implemented in  $0.35\mu\text{m}$  CMOS.

# 6.2 A 1.6GS/s 12b RTZ GaAs RF DAC for Multiple Nyquist Operation

2:00 PM

M-J. Choe, K-H. Baek, M. Teshome Rockwell, Thousand Oaks, CA

RZ current switches are added to a current steering DAC for high-frequency wideband applications to achieve 800MHz bandwidth at 1<sup>st</sup> and 2<sup>nd</sup> Nyquist band without the need for a reverse sinc equalization filter. Implemented in a GaAs HBT process with 4.5μm² minimum emitter area, the DAC dissipates 1.2W at -5V with a 1.6GHz clock and 0dBm typical output power.

# 6.3 A 1.7GHz 3V Direct Digital Frequency Synthesizer with an On-chip DAC in 0.35μm SiGe BiCMOS

2:30 PM

K-H. Baek, E. Merlo, M-J. Choe, A. Yen, M. Sahrling Rockwell, Thousand Oaks, CA

A single-chip direct digital frequency synthesizer with hardware efficient phase-to-amplitude mapping and an integrated DAC achieves over 50dB SFDR in full-Nyquist band at 1.7GHz clock frequency for synthesized output signals up to 850MHz. The IC is implemented in a  $0.35\mu m$  SiGe BiCMOS process and occupies an area of  $4.8\times5.0 mm^2$ . Power efficiency is 1.76 mW/MHz at 3V.

**BREAK 3:00 PM**

# 6.4 A 12b 500MS/s DAC with >70dB SFDR up to 120MHz in 0.18µm CMOS

3:15 PM

K. Doris<sup>1,2</sup>, J. Briaire<sup>1</sup>, D. Leenaerts<sup>1</sup>, M. Vertregt<sup>1</sup>, A. van Roermund<sup>2</sup>

1 Philips, Eindhoven, The Netherlands

<sup>2</sup>Technical University Eindhoven, Eindhoven, The Netherlands

A CMOS current steering 12b 500MS/s 216mW DAC without any additional circuitry to remove errors introduced during the conversion process has >70dB SFDR up to 120MHz above the Nyquist band. This is comparable to state-of-the-art performance requiring additional circuitry, and better than any design without additional circuitry.

## Monday, February 7th 1:30 PM

# 6.5 A 350MHz Low-OSR ΔΣ Current-Steering DAC with Active Termination in 0.13μm CMOS

3:45 PM

M. Clara, W. Klatzer, A. Wiesbauer, D. Straeussnigg Infineon, Villach, Austria

A time-interleaved architecture overcomes the dynamic performance limitations of standard DWA switching. Clocked at 350MHz, the DAC with active output buffer achieves a linearity of 76dB for a signal swing of 1.536V and an effective resolution of 11.9b in a bandwidth of 29.16MHz. It is fabricated in a standard 0.13μm CMOS process and consumes 62mW from a 1.5V supply.

## 6.6 Integrated Stereo $\Delta\Sigma$ Class D Amplifier

4:15 PM

E. Gaalaas¹, B. Liu², N. Nishimura²¹Analog Devices, Bedford, MA²Analog Devices, Tokyo, Japan

A 2×40W (into  $4\Omega$  with a 20V supply) integrated stereo  $\Delta\Sigma$  class D amplifier with 100dB SNR is realized in a 0.6µm CMOS process with DMOS transistors and buried zener diodes. Feedback from power stage outputs gives 0.001% THD and 65dB PSRR. The modulator clock rate is 6MHz, but dynamically adjusted quantizer hysteresis reduces the output data rate to 450kHz, helping achieve 88% efficiency.

#### 6.7 A 22GS/s 6b DAC with Integrated Digital Ramp Generator 4:45 PM

P. Schvan¹, D. Pollex¹, T. Bellingrath²¹Nortel Networks, Ottawa, Canada²Institut fuer Mikroelektronik Stuttgart, Germany

A 22GS/s 6b DAC is presented that includes a digital ramp pattern generator. The DAC core and ramp generator consume 2W and 1.2W respectively operating from 3.3V. The DAC produces a differential signal up to  $1.3V_{\rm pp}$ . DNL<0.5LSB and INL<0.9LSB are measured. The highest glitch energy is 0.5pVs. Settling times are 70 and 40ps for full- and half-scale transitions, respectively.

### 6.8 A 2GHz Mean-Square Power Detector with Integrated Offset Chopper

5:00 PM

M. Kouwenhoven, A. van Staveren National Semiconductor, Delft, The Netherlands

A 2GHz mean-square power detector with integrated chopper is presented. It typically achieves an offset reduction of 14.8dB compared to unchopped, untrimmed units and 12dB reduction of the offset variation over temperature (-40°C to +85°C) compared to laser-trimmed units. The chip is designed in a 0.35 $\mu$ m BiCMOS process, measures 1.5x1.5mm² and draws 8mA from a 2.7V supply.

CONCLUSION 5:15 PM

#### SESSION 7 **NOB HILL**

#### MULTIMEDIA PROCESSING

Lee-Sup Kim, KAIST, Daejeon, Korea Chair:

Associate Chair: Masafumi Takahashi, Toshiba, Kawasaki, Japan

#### 7.1 A 1.3TOPS H.264/AVC Single-Chip Encoder for HDTV Applications

1:30 PM

Y-W. Huang<sup>1</sup>, T-C. Chen<sup>1</sup>, C-H. Tsai<sup>1</sup>, C-Y. Chen<sup>1</sup>, T-W. Chen<sup>1</sup>, C-S. Chen<sup>2</sup>, C-F. Shen<sup>3</sup>, S-Y. Ma<sup>3</sup>, T-C. Wang<sup>4</sup>, B-Y. Hsieh<sup>5</sup>, H-C. Fang<sup>1</sup>, L-G. Chen<sup>1</sup> National Taiwan University, Taipei, Taiwan

<sup>2</sup>Chip Implementation Center, Hsin-Chu, Taiwan

<sup>3</sup>Vivotek, Taipei, Taiwan

<sup>4</sup>Chin Fong Machine Industrial, Chang Hua, Taiwan

<sup>5</sup>MediaTek, Hsin-Chu, Taiwan

An H.264/AVC encoder is implemented on a 31.72mm<sup>2</sup> die with 0.18µm CMOS technology. A four-stage macroblock pipelined architecture encodes 720p 30f/s HDTV videos in real time at 108MHz. The encoded video quality is competitive with reference software requiring 3.6TOPS on a general-purpose processor-based platform.

#### 7.2 An 81MHz 1280x720Pixelsx30f/s MPEG-4 Video/Audio CODEC Processor

2:00 PM

H. Yamauchi, S. Okada, M. Suzuki, Y. Matsuo, Y. Ishii, T. Mori, T. Watanabe, Y. Matsushita Sanyo Electric, Gifu, Japan

A high-definition MPEG-4 CODEC processor capable of encoding 720p images (1280x720 pixels 30f/s) at 81MHz is presented. The CODEC is implemented with only 390k gates and an 80kb SRAM. It is fabricated in a 0.13µm CMOS process on a 5.6mmx5.6mm die.

#### 7.3 An H.264/MPEG-4 Audio/Visual CODEC LSI with Module-Wise Dynamic Voltage/Frequency Scaling 2:30 PM

T. Fujiyoshi, S. Shiratake, S. Nomura, T. Nishikawa, Y. Kitasho, H. Arakida, Y. Okuda, Y. Tsuboi, M. Hamada, H. Hara, T. Fujita, F. Hatori, T. Shimazawa, K. Yahagi, H. Takeda, M. Murakata, F. Minami, N. Kawabe, T. Kitahara, K. Seta, M. Takahashi, Y. Oowaki Toshiba, Kawasaki, Japan

A single-chip H.264/MPEG-4 audio/visual LSI for mobile applications with a module-wise dynamic voltage/frequency scaling architecture is described. This LSI operates even during the voltage/frequency transition with no performance overhead by using a dynamic de-skewing system and an on-chip voltage regulator with slew-rate control. The IC consumes 90mW in decoding QVGA H.264 video at 15f/s and MPEG-4 AAC LC audio simultaneously.

**BREAK 3:00 PM**

#### Monday, February 7th 1:30 PM

#### 7.4 A Streaming Processing Unit for a CELL Processor

B. Flachs', S. Asano', S. Dhong', P. Hofstee', G. Gervais', R. Kim', T. Le', P. Liu', J. Leenstra', J. Liberty', B. Michael, S. Mueller', O. Takahashi', Y. Watanabe<sup>2</sup>, A. Hatakeyama<sup>4</sup>, H. Oh<sup>1</sup>, N. Yano<sup>2</sup> <sup>1</sup>IBM, Austin, TX <sup>2</sup>Toshiba, Austin, TX

<sup>3</sup>IBM, Boeblingen, Germany <sup>4</sup>Sony, Austin, TX

The design of a 4-way SIMD streaming data processor emphasizes achievable performance in area and power. Software controls data movement and instruction flow, and improves data bandwidth and pipeline utilization. The micro-architecture minimizes instruction latency and provides fine-grain clock control to reduce power.

#### A 600MIPS 120mW 70µA Leakage Triple-CPU Mobile 7.5 **Application Processor Chip**

S. Torii', S. Suzuki', H. Tomonaga', T. Tokue', J. Sakai', N. Suzuki', K. Murakami', T. Hiraga', K. Shigemoto', Y. Tatebe', E. Obuchi', N. Kayama', M. Edahiro', T. Kusano', N. Nishi'

<sup>1</sup>NEC, Sagamihara, Japan <sup>2</sup>NEC, Kawasaki, Japan

A triple-CPU mobile application processor is developed on an  $8.95 \text{mm} \times 8.95 \text{mm}$  die in a  $0.13 \mu \text{m}$  CMOS process. The IC integrates 3xARM926 cores, a DSP, several accelerators, as well as strong bus and memory interfaces. It consumes 120mW for digital TV, web browser, and 3D graphics, and 250mW@200MHz for 600MIPS with full processing.

#### 7.6 90nm Low-Leakage SoC Design Techniques for Wireless Applications

4:15 PM

P. Royannez

Texas Instruments, Villeneuve Loubet, France

The new generation of multimedia-application processors requires a drastic leakage reduction to bring the standby current to 50µA. An efficient set of leakage reduction techniques, including power gating, memory retention, voltage scaling, and dual  $V_{\rm t}$  is employed on a 50M transistor, 80mm² IC, fabricated in a 90nm CMOS technology, resulting in a 40x leakage reduction.

#### 7.7 A 100-Channel Analog CMOS Auditory Filter Bank for Speech Recognition

4:45 PM

E. Fragnière<sup>1,2</sup>

Swiss Centre of Electronics and Microtechnology (CSEM),

Neuchâtel, Switzerland

<sup>2</sup>University of Applied Sciences, Fribourg, Switzerland

An ASIC emulates the inner ear as a bank of 100 exponentially distributed asymmetric band-pass filters that roll off at up to 450dB/dec and have individually tunable Q-factors. The output is encoded into an auditory-nerve-like pulsed format on a digital port. The chip is integrated in a 0.5µm process and consumes 2.6mW at 3.3V.

CONCLUSION 5:15 PM

### DISCUSSION SESSIONS

E1: Mobile Imaging: Paradigm Shift or Technology Bubble?

(Salon 7)

Organizer: Boyd Fowler, Agilent Technologies, Santa Clara, CA Moderator: Jed Hurwitz, ST Microelectronics, Edinburgh, Scotland

Since the 1960s telephone companies have tried to develop and market picture-phones without success. Today there are tens of millions of cell phones with imagers being sold worldwide. Will this prove to be another picture-phone failure or is it different this time? What is the application that will make mobile imaging successful? Will mobile imaging replace standalone digital cameras? If mobile imaging is here to stay, how does everyone in the value chain realize a profit?

#### Panelists:

Jinsung Choi, LG Electronics, Seoul, Korea Minoru Etoh, DoCoMo Communications, San Jose, CA Janne Haavisto, Nokia, Tampere, Finland Jason Hartlove, Agilent Technologies, Santa Clara, CA Tadakuni Narabu, Sony, Kanagawa, Japan Stephen A. Noble, Eastman Kodak, Rochester, NY

E2: What Papers Will and Will Not Be at ISSCC2010?

(Salon 8)

Organizer: Axel Thomsen, Silicon Laboratories, Austin, TX

Moderator: David Robertson, Analog Devices, Wilmington, MA

The 1980s and 1990s witnessed great advances in analog integrated circuit design, particularly in CMOS technology. High-resolution circuits such as data converters and high-performance RF CMOS circuits were created. In the future as technology scaling results in sub-1V power supplies, is any transistor level circuit innovation possible or will all innovation be at the system level?

#### Panelists:

Randall Geiger, Iowa State University, Durham Ames, IA Bang Won Lee, ATLab, KyungGi-Do, Korea Dennis Monticelli, National Semiconductor, Santa Clara, CA

Don Shaver, Texas Instruments, Dallas, TX Werner Weber, Infineon, Munich, Germany Bill Redman-White, Philips Semiconductors and Southampton University, Southhampton, United Kingdom

## Monday, February 7<sup>th</sup> 8:00 PM

SE4: Toward the Nanoscale Transistor - Highlights of 2004 Symposium on VLSI Technology

(Salon 9)

Organizer: Takayuki Kawahara, Hitachi, Tokyo, Japan Chair: Shin'ichiro Kimura, Hitachi, Tokyo, Japan

In the nano-scale era, the advantages of bulk-CMOS technology diminish with transistor scaling. Among the difficulties encountered are the ON current limits, the inherent increase in OFF current due to leakage, and manufacturability. For Moore's Law to remain valid, these difficulties must be overcome. Fortunately, as indicated by leading researchers in their fields, new technologies are emerging that address these issues, and appear suitable for nanotechnology implementations.

The papers in this session have been carefully selected from the 2004 Symposium on VLSI Technology. The technologies discussed include: strained-channel technology, 5nm FinFETs, a hybrid technology using a bulk-Si-SOI combination, and a sub-10nm bulk-CMOS transistor. Demonstrated, are devices with 1 to 2mA ON currents with minimal OFF currents. The underlying concepts are revealed, as are the potential for application of each technology.

The intent in presenting this session is to provide to ISSCC attendees the concepts underlying prototype devices, so that circuit designers become better able to contribute to building a nano-scale world.

| <u>Time</u> | <u>Topic</u>                                                                                                                                                                                                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:00        | "An Enhanced 90nm High Performance Technology with<br>Strong Performance Improvements from Stress and<br>Mobility Increase through Simple Process Changes<br>Rajesh B. Khamankar, Texas Instruments,<br>Dallas, TX |

| 8:30        | " <b>5nm-Gate Nanowire FinFET</b> " <b>Fu-Liang Yang</b> , Taiwan Semiconductor,  Manufacturing Company, Hsin-Chu City, Taiwan                                                                                     |